# Drain Current Analysis with Process Parameters Variations of Nanowire TFET

Parveen Kumar<sup>1</sup>, Saurabh Khandelwal<sup>2</sup>, Balwant Raj<sup>3</sup>, Parminder Kaur<sup>4</sup> and Balwinder Raj<sup>5</sup>

<sup>1</sup>Dr. B. R. Ambedkar National Institute of Technology, Jalandhar, 144011, India <sup>2</sup>School of Engineering, Computing & Mathematics, University of Oxford Brookes,UK <sup>3</sup>UIET, Panjab University SSG Regional Centre, Hoshiarpur, 146021, India <sup>4.5</sup>National Institute of Technical Teachers Training and Research, Chandigarh,160019, India

#### Abstract

This paper presents the drain current analyses for the different parameters of Nanowire tunnel field-effect transistor (TFET). The device has been designed using an n-channel  $P^+$ -I-N<sup>+</sup> structure for tunneling junction of TFET with gate-all-around (GAA) Nanowire. The gate length has been taken as 100 nm using silicon Nanowire to obtain the various parameters such as ON-current (I<sub>ON</sub>), OFF-current (I<sub>OFF</sub>), current ratio, and Subthreshold slope (SS) by applying different values of work function at the gate, the radius of Nanowire and oxide thickness of the device. The simulations are performed on Silvaco TCAD which gives a better parametric analysis over conventional tunnel field-effect transistor. The results obtained will be useful for the scientific and research community working in this area.

#### **Keywords**

Drain Current (ID), Gate All Around (GAA), Nanowire (NW), Gaussian doping (GD), TFET.

### 1. Introduction

The regular scaling in metal oxide semiconductor field effect transistors (MOSFETs) is very difficult due to various aspects such as current carrier mechanism (thermal emission of electrons); higher short channel effects (SCEs), high OFF current and limited subthreshold slope (60mV/decade) in the Nanoscale regimes [1]–[8]. The main demerit of MOSFET is Subthreshold Slope (SS) which is defined as rate of increase in output (drain) current with the increase in the gate-source voltage ( $V_{gs}$ ) from 0 volt. The higher SS are effects the supply voltages, which is required for the switching of device from OFF state to ON state [9]–[12]. For the development of new devices in the semiconductor; there is need to be especially low power, lower SS and power efficient device. The tunnel field effect transistor (TFET) is most preferable candidate in the semiconductor industry from the last decade [13]-[18]. The current carrier mechanism of TFET is performed by tunneling instead of thermionic emission. The structure of TFET is in asymmetrical nature (p-i-n) with different material of source and drain (either n-type or p-type). TFET has number of merits which overcomes the problem of MOSFET such as low Subthreshold Slope (SS) which is suitable for low power supply, reduced SCEs [19]–[23] and low OFF-current (I<sub>OFF</sub>) due to band to band tunneling mechanism; but it suffers from low ONcurrent (I<sub>ON</sub>), which is required for high speed operation of the device. So it should be needed that an advance device which mitigates the problem of low I<sub>ON</sub> and operating speed. The Nanowire based TFET structures have the potential to gives the better results in terms of high ON-current and higher operation speed with reduced SCEs [12], [24]-[26]. So we have designed and simulate gate all around Nanowire TFET (NWTFET) and analyze its various parameters such as I<sub>ON</sub>, I<sub>OFF</sub>, ON-OFF current

ORCID: 0000-0001-7392-8844 (A. 1); 0000-0001-7992-3390 (A. 2); 0000-0001-5596-7209 (A. 3); 0000-0002-0908-6803 (A. 4); 0000-0002-3065-6313(A. 5)

Use permitted under Creative Commons License Attribution 4.0 International (CC BY 4.0).

CEUR Workshop Proceedings (CEUR-WS.org)

International Conference on Emerging Technologies: AI, IoT, and CPS for Science & Technology Applications, September 06–07, 2021, NITTTR Chandigarh, India

EMAIL: parveen.eng@gmail.com (A. 1); skhandelwal@brookes.ac.uk (A. 2); b.raj255@gmail.com (A. 3); parm1476@gmail.com (A. 4); balwinderraj@gmail.com (A. 5)

ratio  $(I_{ON}/I_{OFF})$  and SS with the impact of its dimensional parameters such as gate length, oxide thickness and radius of Nanowire.

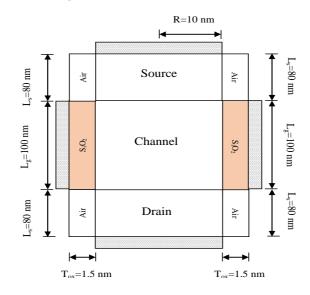

### 2. Device Structure

The structure of designed gate all around Nanowire TFET (NWTFET) is shown in Figure 1. The basic  $p^+$ -i- $n^+$  structure of TFET is used for device designing with Silicon GAA Nanowire. The basic parameters NWTFET taken as gate length ( $L_g$ ) = 100 nm, Nanowire Radius (R) = 10 nm, Source/Drain length ( $L_{s/d}$ ) = 80 nm, thickness of gate oxide ( $T_{ox}$ ) = 1.5 nm with Gaussian doping concentration are used for simulation of the device using Silvaco Atlas Tools.

#### Figure 1: Strcture of NWTFET

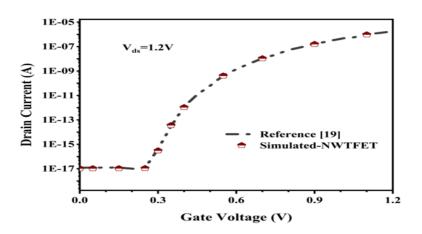

The high source/drain doping concentration, channel doping concentration and gate-workfunction of NWTFET are taken as  $1*10^{-19}$  cm<sup>-3</sup>,  $1*10^{-17}$  cm<sup>-3</sup> and 4.3 eV respectively. The Silicon thickness are maintained under Debye-length;  $as\sqrt{([(\epsilon_si V_T)/q + 60.N])}$ , where as q, N, V<sub>T</sub> represents the charge of electron, concentration and thermal voltage respectively while  $\epsilon_{si}$  refer as dielectric constant [27]. The proposed structure is calibrated with reported conventional TFET structure [19]. The basic parameters of conventional device are taken same as reported in ref [19]. The calibration has been done using plot digitizer tools and Silvaco Simulation Tool. The calibration curve of NWTFET is shown in Figure 2.

Figure 2: Calibration Curve of NWTFET with ref [19]

The different models have been used for simulations such as BTBT model for tunneling, BGN model for the effect of bandgap and FLDMOB for field-dependent mobility as well as FERMI model for Fermi–Dirac statistics with the addition of CVT model. The used parameter for NWTFET designing is illustrating in Table 1.

| Parameter of NWTFET              |                                   |

|----------------------------------|-----------------------------------|

| Parameters                       | Values                            |

| Gate length (Lg)                 | 100 nm                            |

| Work-function of Gate $(\phi_g)$ | 4.3eV                             |

| Thickness of gate oxide (Tox)    | 2.5 nm                            |

| Nanowire Radius (R)              | 20 nm                             |

| Channel Concentration            | $1 \times 10^{17} \text{cm}^{-3}$ |

| Source/Drain Concentration       | $1 \times 10^{19} \text{cm}^{-3}$ |

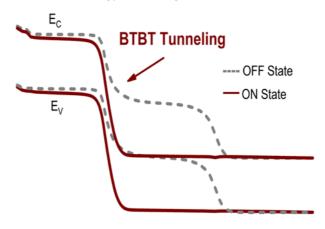

Figure 3. Illustrate the energy band diagrams of NWTFET in ON state and OFF state which is performing as tunneling actions during simulation process. When the gate voltage is equal to zero and greater than zero (~1.5V), device will act as OFF state (dash line) and ON state (solid line) respectively by applying drain-source voltage is 1.0 V as shown in Figure 3. The energy gap between valance band and conduction band is higher in OFF state but lesser in ON state. So the tunneling of electrons has possible only in ON state as shown in energy band diagram.

Figure 3: Energy band diagram of NWTFET

## 3. Result and Simulation

Table 1

The result and simulation of NWTFET are explained in this section by using Silvaco simulation tool. To calculate the different parameters such as drain current, ON/OFF ratio and SS, dimensional parameters has been varied such as gate work-function ( $\phi_g$ ), oxide thickness and radius of Nanowire. The drain current variation of NEFET are observed with the effect/impact of different parameters such as

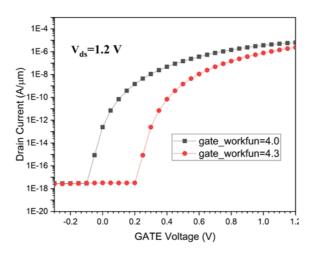

# **3.1** Effect of work-function $(\phi_g)$

Firstly, the I<sub>D</sub> characteristics are observed with different  $\phi_g$  and taken as 4.0 eV and 4.3 eV shown in Figure 4. For the simulation work the gate voltage varied from -0.2 to 1.2 voltage and drain-source voltage (V<sub>ds</sub>) taken as 1.2V. According to Figure 4, the maximum ON current (3.60×10<sup>-6</sup>) and minimum SS (20.25 mV/dec) are observed at  $\phi_g$  =4.0 eV, but OFF (2.45×10<sup>-13</sup>) current is also high

which leads the SCEs. On the other hand lower OFF current is observed at 4.3 eV. So  $\phi_g = 4.3$  has been taken for proposed device for minimum SCEs.

Figure 4: Effect of gate work-function on drain current

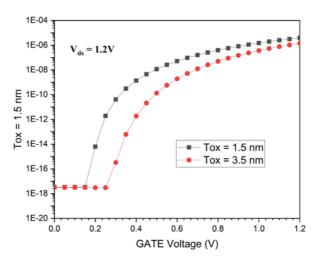

# 3.2 Effect of oxide thickness (T<sub>ox</sub>)

Secondly, the I<sub>D</sub> characteristics are observed with different  $T_{ox}$  (1.5 nm and 3.5 nm). Figure 5 illustrates the simulation work of NWTFET on drain current with the impact of different  $T_{ox}$  at 1.2V drain-source voltage. It is observed that better parametric value of I<sub>D</sub> and current ratio with minimum SS (19.40) at Tox=1.5 nm. During the simulation process  $\phi_g$ , R and  $T_{ox}$  has been taken as 4.3 eV, 20 nm and 3.5 nm respectively. The minimum value oxide thickness has given good parametric values and lesser leakage current in the device.

Figure 5: Drain current variation due to effect of Tox

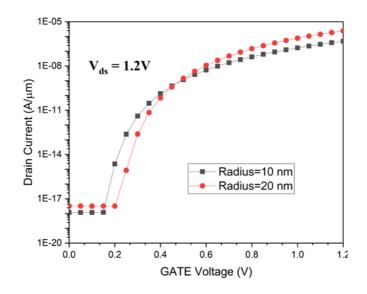

# 3.3 Effect of Nanowire Radius (R)

The drain current variation with the effect of nanowire radiu are shown in Figur 6. According to characteristics curve it observed that higher  $I_{ON}$  (7.63×10<sup>-7</sup>) at R= 20 nm, but the  $I_{OFF}$  current is also higher at this stage. Due to R variation on NWTFET the better SS (15. 22) has been archived on 10 nm. During to simulation work, gate voltage is varied from 0 to 1.5 and  $V_{ds}$ =1.2.

Figure 5: Drain current variation due to effect of Radius (R)

The detailed observed parametric values are given in Table 2.

| Parameters of NWTFET     | after Simulation      |                         |                        |             |

|--------------------------|-----------------------|-------------------------|------------------------|-------------|

| Parameter                | $I_{ON}(A/\mu m)$     | I <sub>OFF</sub> (Α/μm) | $I_{ON}/I_{OFF}$ Ratio | SS (mV/dec) |

| $\phi_g$ = 4.0 eV        | 3.60×10 <sup>-6</sup> | 2.45×10 <sup>-13</sup>  | $1.47 \times 10^{7}$   | 20.25       |

| φ <sub>g</sub> = 4.3 eV  | 7.63×10 <sup>-7</sup> | 3.23×10 <sup>-18</sup>  | 2.36×10 <sup>11</sup>  | 20.32       |

| T <sub>ox</sub> = 1.5 nm | 2.05×10 <sup>-6</sup> | 2.95×10 <sup>-19</sup>  | 6.94×10 <sup>12</sup>  | 19.40       |

| T <sub>ox</sub> = 3.5 nm | 1.71×10 <sup>-6</sup> | 7.40×10 <sup>-19</sup>  | 2.31×10 <sup>12</sup>  | 25.67       |

| R = 10 nm                | 1.69×10 <sup>-7</sup> | 1.17×10 <sup>-18</sup>  | 1.45×10 <sup>11</sup>  | 15.22       |

| R = 20 nm                | 7.63×10 <sup>-7</sup> | 3.23×10 <sup>-18</sup>  | 2.36×10 <sup>11</sup>  | 20.32       |

| Table 2                               |

|---------------------------------------|

| Parameters of NWTFET after Simulation |

# 4. Conclusion

The device NWTFET has been designed and simulated using Gaussian doping profile and analyzed parametric variations of  $I_{ON}$ ,  $I_{OFF}$ ,  $I_{ON}/I_{OFF}$  and SS. The simulated results have also shows the effect on drain-current ( $I_d$ ) with impact of Tox, R and  $\phi_g$  of the device. The most suitable parametric value are observed such as  $I_{ON} = 3.60 \times 10^{-6} \text{ A}/\mu\text{m}$ ,  $I_{OFF} = 2.95 \times 10^{-19} \text{ A}/\mu\text{m}$ , SS = 15.22 mV/dec and  $I_{ON/OFF} = 6.94 \times 10^{12}$ . The proposed NWTFET device structure will be suitable for low power applications.

## 5. Acknowledgment

We thank the Group, department of Electronics and Communication Engineering, Dr. B.R. Ambedkar NIT Jalandhar and VLSI Design Group NITTTR Chandigarh for their interest in this work and useful comments to draft the final form of the paper. The support of SERB, Government of India, and Project (EEQ/2018/000444) is gratefully acknowledged. We would like to thank NIT Jalandhar and NITTTR Chandigarh for lab facilities and research environment to carry out this work.

## 6. References

- [1] C. Duvvury, "A guide to short-channel effects in MOSFETs," *IEEE Circuits Devices Mag.*, vol. 2, no. 6, pp. 6–10, 1986.

- [2] K. P. Cheung, "On the 60 mV/dec@ 300 K limit for MOSFET subthreshold swing," in Proceedings of 2010 International Symposium on VLSI Technology, System and Application, 2010, pp. 72–73.

- [3] M. G. Bardon, H. P. Neves, R. Puers, and C. Van Hoof, "Pseudo-two-dimensional model for double-gate tunnel FETs considering the junctions depletion regions," *IEEE Trans. Electron Devices*, vol. 57, no. 4, pp. 827–834, 2010.

- [4] M. Xu *et al.*, "Improved short channel effect control in bulk FinFETs with vertical implantation to form self-aligned halo and punch-through stop pocket," *IEEE Electron Device Lett.*, vol. 36, no. 7, pp. 648–650, 2015.

- [5] K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand, "Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits," *Proc. IEEE*, vol. 91, no. 2, pp. 305–327, 2003.

- [6] R. Narang, M. Gupta, and M. Saxena, "Investigation of dielectric-modulated double-gate junctionless MOSFET for detection of biomolecules," in 2013 Annual IEEE India Conference (INDICON), 2013, pp. 1–6.

- [7] Q. Chen, B. Agrawal, and J. D. Meindl, "A comprehensive analytical subthreshold swing (S) model for double-gate MOSFETs," *IEEE Trans. Electron Devices*, vol. 49, no. 6, pp. 1086–1090, 2002.

- [8] T. Chawla, M. Khosla, and B. Raj, "Design and simulation of triple metal double-gate germanium on insulator vertical tunnel field effect transistor," *Microelectronics J.*, p. 105125, 2021.

- [9] R. Gandhi, Z. Chen, N. Singh, K. Banerjee, and S. Lee, "Vertical Si-Nanowire \$ n \$-Type Tunneling FETs With Low Subthreshold Swing (\$\leq\hbox {50}\\hbox {mV/decade} \$) at Room Temperature," *IEEE Electron Device Lett.*, vol. 32, no. 4, pp. 437–439, 2011.

- [10] S. Sharma, B. Raj, and M. Khosla, "Comparative Analysis of MOSFET CNTFET and NWFET for High Performance VLSI Circuit Design," *A Rev. J. VLSI Des. Tools Technol.*, vol. 6, no. 2, pp. 19–32, 2016.

- [11] S. K. Sharma, B. Raj, and M. Khosla, "A Gaussian approach for analytical subthreshold current model of cylindrical nanowire FET with quantum mechanical effects," *Microelectronics J.*, vol. 53, pp. 65–72, 2016.

- [12] S. K. Sharma, P. Kumar, B. Raj, and B. Raj, "In1-xGaxAs Double Metal Gate-Stacking Cylindrical Nanowire MOSFET for highly sensitive Photo detector," 2021.

- [13] S. Kumar and B. Raj, "Simulations and modeling of TFET for low power design," in Handbook of Research on Computational Simulation and Modeling in Engineering, IGI Global, 2016, pp. 640–667.

- [14] M. J. Kumar and S. Janardhanan, "Doping-less tunnel field effect transistor: Design and investigation," *IEEE Trans. Electron Devices*, vol. 60, no. 10, pp. 3285–3290, 2013.

- [15] G. Wadhwa and B. Raj, "Design, Simulation and Performance Analysis of JLTFET Biosensor for High Sensitivity," *IEEE Trans. Nanotechnol.*, vol. 18, pp. 567–574, 2019.

- [16] H. Lu and A. Seabaugh, "Tunnel field-effect transistors: State-of-the-art," *IEEE J. Electron Devices Soc.*, vol. 2, no. 4, pp. 44–49, 2014.

- [17] W. Y. Choi, B.-G. Park, J. D. Lee, and T.-J. K. Liu, "Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec," *IEEE Electron Device Lett.*, vol. 28, no. 8, pp. 743–745, 2007.

- [18] S. Singh, M. Khosla, G. Wadhwa, and B. Raj, "Design and analysis of double-gate junctionless vertical TFET for gas sensing applications," *Appl. Phys. A*, vol. 127, no. 1, pp. 1– 7, 2021.

- [19] Z. X. Chen *et al.*, "Demonstration of tunneling FETs based on highly scalable vertical silicon nanowires," *IEEE Electron Device Lett.*, vol. 30, no. 7, pp. 754–756, 2009.

- [20] N. Kumar and A. Raman, "Performance Assessment of the charge-plasma-based cylindrical GAA Vertical nanowire TFET with Impact of interface trap charges," *IEEE Trans. Electron*

Devices, vol. 66, no. 10, pp. 4453–4460, 2019.

- [21] S. Badgujjar, G. Wadhwa, S. Singh, and B. Raj, "Design and analysis of dual source vertical tunnel field effect transistor for high performance," *Trans. Electr. Electron. Mater.*, vol. 21, no. 1, pp. 74–82, 2020.

- [22] M.-C. Sun *et al.*, "Scalable embedded Ge-junction vertical-channel tunneling field-effect transistor for low-voltage operation," in *2010 IEEE Nanotechnology Materials and Devices Conference*, 2010, pp. 286–290.

- [23] P. Kumar and S. K. Sharma, "Comparative Analysis of Nanowire Tunnel Field Effect Transistor for Biosensor Applications," *Silicon*, pp. 1–8, 2020.

- [24] M. Rahimian and M. Fathipour, "Junctionless nanowire TFET with built-in NPN bipolar action: Physics and operational principle," *J. Appl. Phys.*, vol. 120, no. 22, p. 225702, 2016.

- [25] S. Mokkapati, N. Jaiswal, M. Gupta, and A. Kranti, "Gate-all-around nanowire junctionless transistor-based hydrogen gas sensor," *IEEE Sens. J.*, vol. 19, no. 13, pp. 4758–4764, 2019.

- [26] S. K. Sharma, A. Jain, and B. Raj, "Analysis of triple metal surrounding gate (TM-SG) III–V nanowire MOSFET for photosensing application," *Opto-Electronics Rev.*, vol. 26, no. 2, pp. 141–148, 2018.

- [27] G. Wadhwa and B. Raj, "Parametric variation analysis of symmetric double gate charge plasma JLTFET for biosensor application," *IEEE Sens. J.*, vol. 18, no. 15, pp. 6070–6077, 2018.