Belgacem BEN HEDIA, CEA, LIST, France Florin Popentiu VLADICESCU, University of Oradea, Romania

# VECoS'2015

# Verification and Evaluation of Computer and Communication Systems

9<sup>th</sup> International Workshop Bucharest, Romania, September 10-11, 2015 Proceedings

©Copyright 2015 for the individual papers by the papers' authors. Copying permitted for private and academic purposes. This volume is published and copyrighted by its editors.

These proceedings are published online by the editors as Volume 1431 at CEUR Workshop Proceedings ISSN 1613-0073 http://ceur-ws.org/Vol-1431

### PREFACE

These are the proceedings of the 9<sup>th</sup> International Workshop on Verification and Evaluation of Computer and Communication Systems (VECoS'2015) held the 10<sup>th</sup> and 11<sup>th</sup> of September 2015 at the University POLITEHNICA of Bucharest that is the main organizer together with the support of MeFoSyLoMa group and Formal Methods Europe.

The International Workshop on Verification and Evaluation of Computer and Communication Systems (VECoS) was created by an Euro-Maghrebian network of researchers in computer science. Its first edition, VECoS 2007, took place in Algiers, VECoS 2008 in Leeds, VECoS 2009 in Rabat, VECoS 2010 in Paris, and VECoS 2011 in Tunis, VECoS 2012 in Paris, VECoS 2013 in Florence and VECoS 2014 in Bejaia. The aim of the VECoS workshop is to bring together researchers and practitioners, in the areas of verification, control, performance, quality of service, dependability evaluation and assessment, in order to discuss the state-of-the-art and the challenges in modern computer and communication systems in which functional and extra-functional properties are strongly interrelated. Thus, the main motivation for VECoS is to encourage the cross-fertilization between the various formal verification and evaluation approaches, methods and techniques, and especially those developed for concurrent and distributed hardware/software systems. Beyond its technical and scientific goals, another main purpose of VECoS is to promote collaboration between participants in research and education in the area of computer science and engineering. We welcome contributions describing original research, practical experience reports and tool descriptions/demonstrations in the areas of verification, control, performance, quality of service and dependability evaluation.

The invited speakers for VECoS 2015 are: Liliana CUCU-GROSJEAN from AOSTE, INRIA Paris-Rocquencourt, France, Gabriel CIOBANU from Romanian Academy, ICS, Iasi, Romania and Mohamed KAÂNICHE from LAAS, Toulouse, France.

We received 15 high-quality contributions. For each paper three to five reviews were made. The program committee has accepted 9 papers for full presentation.

Without support of our academic and corporate sponsors, the enormous efforts of authors, reviewers, steering committee and the local organizational team this workshop wouldn't provide such an interesting booklet.

We thank the authors for their submissions and the program committee for their hard work.

September 2015

Belgacem BEN HEDIA and Florin Popentiu VLADICESCU

#### ORGANIZING COMMITTEE

Professor Nicolae Tăpus, Computer Science Department, The Faculty of Automatic Control and Computer Science, University POLITEHNICA of Bucharest, Bucharest, Romania Professor Viorel-Puiu Paun, Faculty of Applied Sciences, University POLITEHNICA of Bucharest, Bucharest, Romania

#### STEERING COMMITTEE

Hassane Alla , GIPSA Lab INPG Grenoble Djamil Aissani, LAMOS, Université de Bejaia Kamel Barkaoui , CEDRIC CNAM Paris (**Chair**) Hanifa Boucheneb, Veriform, Ecole Polytechnique de Montréal Francesco Flammini, Ansaldo STS, Milano Mohamed Kaaniche, LAAS CNRS, Toulouse Bruno Monsuez , ENSTA - UIIS, Paris Nihal Pekergin , LACL UPEC, Créteil Denis Poitrenaud, LIP6 UPMC, Paris Tayssir Touili, LIAFA, Université Paris Diderot

#### **PROGRAM COMMITTEE**

Bernhard K. Aichernig, ISF, Graz Djamil Aissani, LAMOS, Bejaia Yamine Ait Ameur, IRIT/ENSEEIHT, Toulouse Otmane Ait Mohamed, Concordia University, Montréal Hassane Alla, GIPSA, Grenoble Lamia Atma Djoudi, Synchrone Technologies, Paris Kamel Barkaoui, Cedric Cnam, Paris Zohra Bakkoury, EMI EAMPIS, Rabat Belgacem Ben Hedia, LIST-CEA, Saclay (co-chair) Saddek Bensalem, VERIMAG Grenoble, France Simon Bliudze, EPFL, Lausanne Jean-Louis Boimond, LARIS, Angers Patrice Bonhomme, LI, Tours Abdelmadjid Bouabdallah, Heudiasyc Lab, Compiegne Hanifa Boucheneb, Polytechnique Montréal Florian Brandner, ENSTA ParisTech, Saclay Carla Ceatzu, University of Cagliari Tijani Chahed, Telecom SudParis, Evry Feng Chu, IBISC, Evry Isabel Demongodin, LSIS Marseille Josée Desharnais, Université Laval, Quebec Karim Djouani, LISSI UPEC, Créteil Mohamed Escheikh, ENIT, Tunis Alessandro Fantecchi, Unifi, Italy Francesco Flammini, Ansaldo STS, Milano Mohamed Ghazel, INRETS, Villeneuve d'Ascq Latéfa Ghomri, University of Tlemcen. Bernd Heidergott, VU Amsterdam University Serge Haddad, LSV Cachan Awatef Hicheur Cairns, Altran Research, Velizy Malika Ioulalen, USTHB Alger

Mohamed Jmaïel, ENSI, Sfax Mohamad Jaber, AUB, Beyrouth Jorge Julvez, University of Zaragoza Mohamed Kaaniche, LAAS, Toulouse Lars Michael Kristensen, Bergen Univ. College, Bergen Bechir Ktari, Université Laval, Québec Gaiyun Liu, Xidian Univ., Xi'an Borhen Marzougui, ECT, Abu Dhabi Mourad Maouche, Philadephia University, Amman Louiza Bouallouche Medjkoune, LAMOS, Bejaia Bruno Monsuez, ENSTA ParisTech, Saclay Mohamed Mosbah, LaBRI, Bordeaux Safia Nait-Bahloul, LITIO, Université d'Oran Meriem Ouederni, IRIT, Toulouse Claire Pagetti, ONERA, Toulouse Vladimir Paun, ENSTA ParisTech, Palaiseau Nihal Pekergin, LACL, Créteil Olivier Perrin, INRIA-LORIA, Nancy Denis Poitrenaud, LIP6, Paris Florin Popentiu Vladicescu, Univ. of Oradea (co-chair) Riadh Robbana, INSAT, Tunis Zaïdi Sahnoun, LIRE, Constantine Zohra Sbaï, ENIT, Tunis Larbi Sekhri, Univ. es Senia, Oran Nadia Tawbi, Université Laval, Quebec Thouraya Tebibel, ESI, Alger Ferucio Laurentiu Tiplea, University of Iasi Tayssir Touili, LIPN Villetaneuse Farouk Toumani, LIMOS, Clermont-Ferrand Karsten Wolf, Universitaet Rostock

# CONTENTS

| Ι  | Session: Control and Diagnosis                                                                                                                                       | 7   |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | Resilience Assessment: Accidental and Malicious Threats ( <i>Invited talk</i> )      Mohamed KAÂNICHE                                                                | 9   |

|    | Fault Diagnosis of P-Time Labeled Petri Net Systems      Patrice BONHOMME                                                                                            | 11  |

|    | Combining Enumerative and Symbolic - Techniques for Diagnosis of Discrete-Event Systems<br><i>Abderraouf</i> BOUSSIF, <i>Mohamed</i> GHAZEL and Kais KLAI            | 23  |

| II | Session: Program verification                                                                                                                                        | 35  |

|    | Probabilistic Approaches for Time Critical Embedded Systems ( <i>Invited talk</i> )<br><i>Liliana</i> CUCU-GROSJEAN                                                  | 37  |

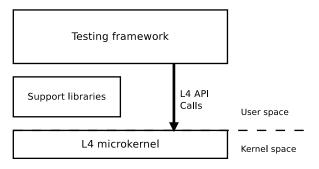

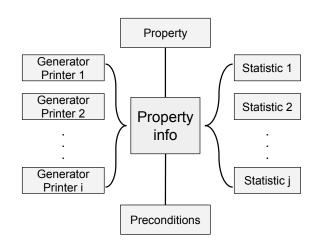

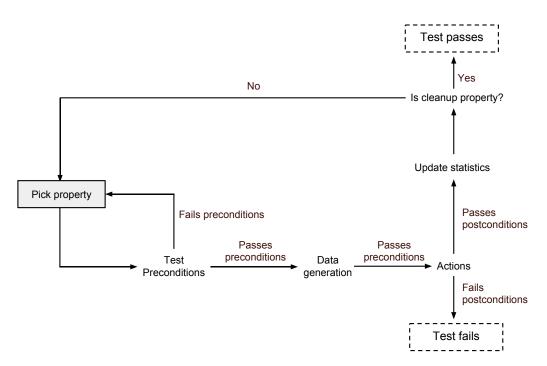

|    | Towards the Property-Based Testing of an L4 Microkernel API<br>Cosmin DRAGOMIR, Lucian MOGOSANU, Mihai CARABAS, Razvan DEACONESCU and Nicolae TAPUS                  | 39  |

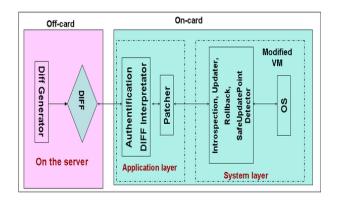

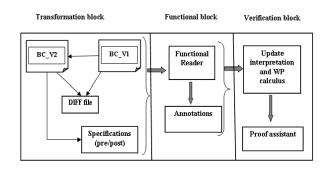

|    | An Approach for Formal Verification of Updated Java Bytecode Programs<br>Razika LOUNAS, Mohamed MEZGHICHE and Jean-Louis LANET                                       | 51  |

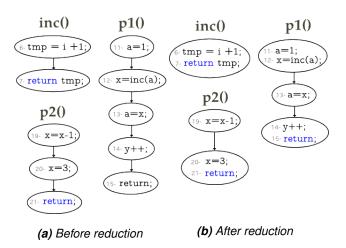

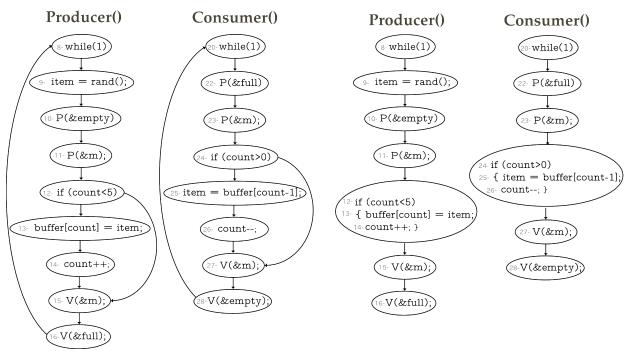

|    | State Space Reduction Strategie for Model Checking Concurrent C Programs         Amira METHNI, Matthieu LEMERRE, Belgacem BEN HEDIA, Serge HADDAD and Kamel BARKAOUI | 65  |

| II | I Session: Performance evaluation                                                                                                                                    | 77  |

|    | Timeout Interaction and Migration in Distributed Systems ( <i>Invited talk</i> ) <i>Gabriel</i> CIOBANU                                                              | 79  |

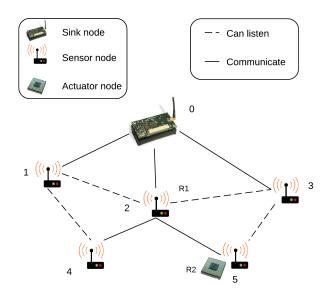

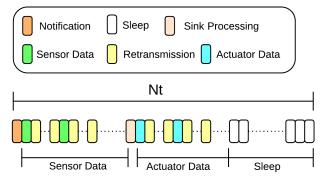

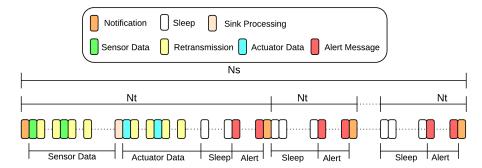

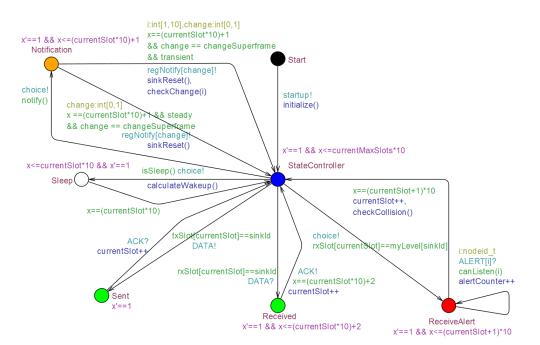

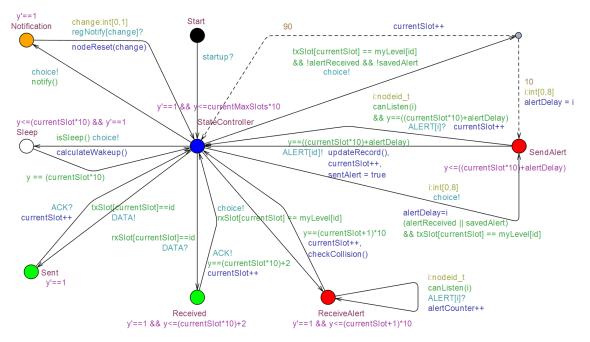

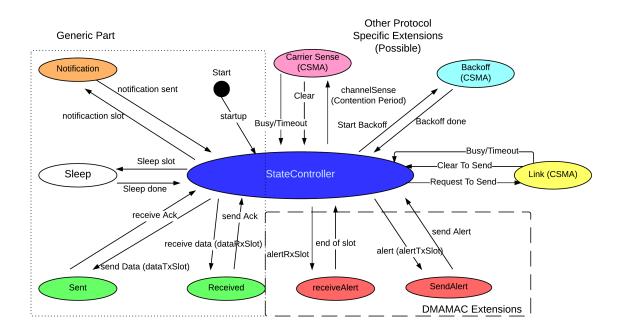

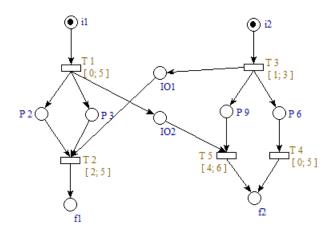

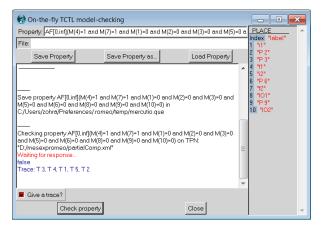

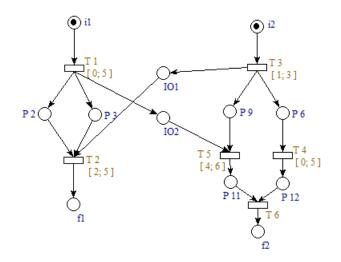

|    | Model-Based Verification of the DMAMAC Protocol for Real-time Process Control<br>Admar Ajith Kumar SOMAPPA, Andreas PRINZ and Lars KRISTENSEN                        | 81  |

|    | On quantitative Analysis of Time Open Workflow Nets and Parametric Extension<br>Zohra SBAï and Kamel BARKAOUI                                                        | 97  |

|    | Verification of Bounded Real-Time Distributed Systems With Mobility         Bogdan AMAN and Gabriel CIOBANU                                                          | 109 |

Part I

# Session: Control and Diagnosis

# Resilience Assessment: Accidental and Malicious Threats

Mohamed Kaâniche

CNRS; LAAS; Université de Toulouse – 7, Avenue du colonel Roche, F-31077 Toulouse, France Université de Toulouse; UPS; INSA; INP; LAAS; F-31077 Toulouse, France mohamed.kaaniche@laas.fr

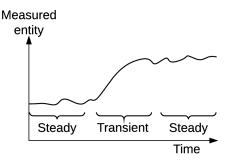

A large body of research has been dedicated to the analysis, assessment and protection of cyberphysical systems and critical infrastructures against potential threats that might affect the dependability, the security or the resilience of the services delivered to the users. Traditionally, accidental and malicious threats have been taken into account separately. In this talk we will address the challenges raised by the resilience assessment and analysis of such systems considering accidental and malicious threats in an integrated way and we will present some examples of research studies carried out in this context.

Critical infrastructures, resilience, assessment, accidental threats, malicious threats

#### 1. SUMMARY

In the past decade, several concerns have been raised about the vulnerability of critical infrastructures and cyber-physical systems and their efficient protection in the presence of accidental and malicious threats (Rahman et al. 2009).

Historically, most of the efforts were dedicated to the protection of critical infrastructures against accidental faults and natural disasters with a specific focus on safety. The situation changed significantly after the September 11, 2001 tragic events that led to increased international concerns about the security and robustness of critical infrastructures in response to evolving malicious threats

The vulnerability of critical infrastructures has increased as a result of the wider use of open networks and information infrastructures, and the proliferation of vulnerable operating systems and control devices. Recent events targeting critical infrastructures show that the threat is real. A widely reported example is the Stuxnet sophisticated malware discovered in July 2010 that targeted specific industrial computer control equipment and software, used for instance in nuclear power plants in Iran [(Langner 2011).

A large body of research has been dedicated to the analysis, assessment and protection of cyberphysical systems and critical infrastructures against potential threats that might affect the dependability, the security or the resilience of the services delivered to the users. The resilience term is used differently, by different communities. It is defined in (Laprie 2011) as the persistence of service delivery that can justifiably be trusted, when facing changes.

Traditionally, accidental and malicious threats have been taken into account separately. In this talk we will address the challenges raised by the resilience assessment and analysis of such systems considering accidental and malicious threats in an integrated way and we will present some examples of research studies carried out in this context.

In particular this objective has been addressed in the context of the CRUTIAL project (http://crutial.rse-web.it/) considering the example of power grid critical infrastructures and the associated information infrastructures dedicated to their management and control.

CRUTIAL focussed on the failures resulting from interdependencies between these infrastructures. The characterization of such failures and the modelling of their impact on relevant properties of power systems have been investigated by means of models at different abstraction levels: i) from a very abstract view expressing the essence of the typical phenomena due to the presence of interdependencies, ii) to an intermediate detail level representing in a rather abstract way the structure of the infrastructures, in some scenarios of interest, iii) to a quite detailed level where the infrastructures components and their interactions are investigated at a finer grain, considering elementary events occurring at the components level and analysing their impact at the system level.

Accordingly, the proposed resilience assessment framework (Kaâniche et al. 2009) is based on a hierarchical modelling approach that accommodates the composition of different types of models and formalisms, including generalized stochastic Petri nets, fault trees, Stochastic Well formed Nets, and Stochastic Activity Networks. Additionally, a new formalism called "Dependent Automata" has been developed to provide a rigorous definition of interdependencies related failures. Also, unified models for describing cascading and escalating failures considering accidental and malicious threats in an integrated way have been defined (Laprie et al. 2007)

Besides these models, the CRUTIAL project resilience assessment activities included architecture validation activities as well as testbed based experiments to analyse the impact of different attack scenarios on control applications.

We will outline some of the results obtained in the context of this project and discuss some open research problems.

### BIO

Mohamed Kaâniche has been at LAAS-CNRS, Toulouse, France, since 1988 where he currently holds a position of "Directeur de Recherche", heading the Dependable Computing and Fault Tolerance Group. From March 1997 to February 1998, he was a Visiting Research Assistant Professor at the University of Illinois at Urbana-Champaign, IL, USA.

His research addresses the dependability and security assessment of hardware and software fault tolerant computer systems and critical infrastructures, using analytical modelling and experimental measurement techniques.

He has been involved in several national and European research projects and acted as a consultant for companies in France and as an expert for the European Commission. He has served on program and organization committees of international dependability related conferences. He was Program Chair of PRDC-2004, EDCC-5, DSN-PDS 2010, LADC-2011 and SAFECOMP- 2013. He is General co-Chair of DSN-2016 that will be held in Toulouse, France in June 2016.

# 3. REFERENCES

- Kaâniche, et al. (2009) CRUTIAL Project Deliverable D16 - Final version of the modelling framework. http://crutial.rseweb.it/Dissemination/DELIVERABLES-OF-THE-PROJECT.asp

- Laprie, Jean-Claude, Kanoun, Karama, Mohamed Kaâniche, (2007) Modelling interdependencies between Electricity and Information Infrastructures. The 26th International Conference on Computer Safety, Reliability, and Security (SAFECOMP-2007), Nuremberg, Germany, LNCS 4680, Springer, pp. 54-67.

- Laprie, Jean-Claude "From Dependability to Resilience", IEEE International Conference on Dependable Systems and Networks (DSN-2008), Supplemental volume, Anchorage, Alaska, USA, pp. G8-G9, 2008.

- Langner, R. "Stuxnet: Dissecting a Cyberwarfare Weapon," *IEEE Security & Privacy*, vol. 9, no. 3, 2011, pp. 49–51.

- Rahman, H.A., Beznosov, K., Marti, J.R., "Identification of sources of failures and their propagation in critical infrastructures from 12 years of public failure reports", Int. Journal on Critical Infrastructures, vol.5, n°3, 2009

# Fault Diagnosis of P-Time Labeled Petri Net Systems

Patrice Bonhomme University François-rabelais CNRS, LI EA 6300, OC ERL CNRS 6305 64 avenue Jean Portalis 37200 Tours France bonhomme@univ-tours.fr

This paper focuses on the fault diagnosis problem of systems modeled with P-time labeled Petri nets with partial information. Indeed, the set of transitions is partitioned into those labeled with the empty string  $\epsilon$  called silent (as their firin cannot be detected) including the faulty transitions and the observable ones. The proposed approach is based on the synthesis of a function called diagnoser allowing to determine the diagnosis state of the system based on the current observation. The novelty of the developed approach resides in the fact that, although the time factor is considered as intervals, the diagnoser is computed thanks to the underlying untimed Petri net structure of the P-time labeled model considered. Furthermore, the method relies on the schedulability analysis of particular firin sequences exhibited by the analysis of the obtained diagnoser and does not require the building of the state class graph.

Discrete event systems. Petri nets. Time labeled systems. Observability. State estimation. Fault diagnosis.

#### 1. INTRODUCTION

The correct behavior of a real-world application is the ultimate requirement, particularly for systems such as communication protocols, manufacturing and real-time systems. Indeed, a drift from an expected behavior can be of crucial importance and can even lead, in extreme cases, to severe consequences including human losses. So, knowing the current state of a system in order to take the appropriate decisions and determining the malfunction of a system component are nowadays fundamental issues.

From a practical point of view, associating a dedicated sensor to each variable of interest in order to monitor its internal state is inconceivable. This restriction, due to economical or physical accessibility reasons leads to a system analysis in presence of uncertainties as the state information cannot be directly obtained. This particularity has gave rise to the introduction of the observers paradigm in the classical system theory. Indeed, an observer can be viewed as a mechanism allowing to estimate or reconstruct the internal state of a system based on some measurements. From a discrete event dynamic systems point of view and more precisely from a Petri net (PN on short) perspective this issue corresponds to the estimation of a PN marking based on some event observations. Thus, being given a sequence of observed events (called word or trace) the challenge consists in determining if a fault has occurred, eventually or for sure!

It can be noticed that the problems of fault diagnosis has receive extensive attention these recent years and particularly in the framework of automata models and regular languages (Sampath et al. (1995), Cassandras and Lafortune (2008), Lin (1994), Cassez and Tripakis (2008)) but there are few studies in the time discrete event systems context.

A preliminary version of this paper was presented in (Bonhomme (2014)) where an approach allowing to estimate the marking of a P-time labeled Petri net (P-TLPN) system based on the observation of particular labels was presented. The plant observation is given by a set of labels whose occurrence can be detected/observed by an external agent (called observer or estimator) - these particular labels are associated to observable transitions. The other transitions, the unobservable ones (called silent transitions) are labeled with the empty string  $\epsilon$ .

In this extended and enriched version, a fault diagnosis problem is solved thanks to the introduction of a function called diagnoser which associates to each observation a diagnosis state. In the proposed technique the set of unobservable transitions is further partitioned into the set of faulty transitions and the set of regular ones. The regular transitions are unobservable and non faulty.

The proposed approach does not require the state class graph construction and consequently it is designed to alleviate the state space explosion problem. Indeed, the construction of the considered state observer is based on the analysis of the underlying untimed PN structure of the P-time labeled PN considered.

In particular, the following four assumptions are made:

- 1. the net structure and the initial marking are known,

- 2. the fault model is known,

- 3. the underlying untimed PN, of the P-TLPN considered is bounded,

- 4. the Petri net induced by the set of unobservable transitions does not contain circuit of null length.

Note that this latter assumption is adopted to exclude the situation where an infinit of actions may take place in a finit amount of time: it prevents the net induced by the set of unobservable transitions from being Zeno (Hadjidj et al. (2007)) which is in contradiction with a diagnosability scheme. In addition, there is no assumption on the backward conflic freeness of the subnet induced by the set of unobservable transitions as in (Giua et al. (2007)).

The paper is organized as follows: after an overview of the relevant literature in the next section, a brief reminder of the basics of untimed Petri nets followed by a formal definitio of P-time labeled Petri nets is realized in the third section. Section four covers the procedure of estimation and the construction of the state observer. The schedulability analysis of the occurrence sequence highlighted by the state observer and its application to the estimation problem are studied in the fift section. In the sixth section the fault diagnosis problem is solved. Section seven presents an illustration of the developed method and the last section concludes the paper and gives suggestions for future research.

### 2. LITERATURE REVIEW

For discrete event system (DES) state estimation has been addressed by several researchers. For instance, in (Giua et al. (2007)) the authors deal with the marking estimation of a labeled Petri net system. Thanks to structural assumptions on the subnet induced by the set of unobservable transitions, they propose an algebraic characterization of the set of consistent markings once a sequence is observed.

In the framework of fault detection or fault diagnosis several approaches can also be found in the literature fault diagnosis is closed to the state estimation problem. Note that a complete survey of fault diagnosis methods for DES can be found in (Zaytoon and Lafortune (2013)). In (Cabasino et al. (2010)) the authors proposed a diagnosis approach based on the concept of basis marking and justificatio under the acyclicity assumption of the unobservable subnet of the system considered. Intuitively, for an observed sequence (word)  $\omega$ , a justificatio can be thought as the set of minimal (in terms of firin vector) unobservable transitions interleaved with  $\omega$  necessary to complete  $\omega$  into a fireable sequence on the net considered, from the initial marking. They extended their work in (Cabasino et al. (2014)) to provide a diagnosability approach for bounded labeled PN by introducing two graphs, namely the modifie basis reachability graph (MBRG) and the basis reachability diagnoser (obtained from the MBRG). Necessary and sufficien conditions for diagnosability are given but the construction of the two graphs is of exponential complexity with respect to the structure of the PN considered and its initial marking.

There are relatively few works in this topic in the time discrete event systems scheme where the time factor is modeled as intervals, so, numerous problems are still open. Concerning the time Petri net model of Merlin (Merlin and Faber (1976)), the authors in (Basile et al. (2013)) proposed a procedure for estimating the marking of the model in presence of unobservable transitions. They introduced a modifie state class graph which captures the required information on the possible evolution of the system starting from a given initial marking. Thanks to this graph, being given a timed sequence and a time instant, the set of markings consistent with the current observation is determined via integer linear programming techniques. The approach is restricted to bounded time Petri nets.

In a recent paper, the authors in (Basile et al. (2015)) extend the previously mentioned approach developed in (Basile et al. (2013)) to deal with the state estimation and the fault diagnosis problem for systems modeled by time PN augmented with labels.

The authors in (Wang et al. (2013)), thanks to a fault diagnosis graph (FDG) which is a truncation of the conventional state class graph (SCG) (Berthomieu and Diaz (1991)), developed an online technique for the fault diagnosis of systems modeled by unlabeled time Petri nets. The FDG is constructed incrementally with respect to the current observation and its number of states can be, in the worst case, the same as the one of the traditional state class graph. Indeed, the FDG is obtained from the SCG by only keeping the information required for the evaluation of the fault states and the authors concentrate on the sequence information and remove the irrelevant state classes (i.e., which are not used in the fault diagnosis). Intuitively, the state classes which are obtained after the firin of an unobservable transition are discarded as the diagnosis state is updated after an observation.

The acyclicity assumption of the subnet induced by the unobservable transitions is also considered. The authors further extend the method in (Wang et al. (2014)) by using reduction rules and model checking techniques.

#### 3. PETRI NETS

#### 3.1. Untimed Petri Nets

The reader unfamiliar with Petri nets can refer to (Murata (1989)), in the following only the basic notions are recalled.

A Place/Transition net (P/T net) is a structure N = (P, T, Pre, Post), where P is a set of m places; T is a set of n transitions.  $Pre : P \times T \to \mathbb{N}$  and  $Post : P \times T \to \mathbb{N}$  are the pre and post incidence functions that specify the arcs; C = Post - Pre is the incidence matrix. The preset and postset of a node  $X \in P \cup T$  are denoted  $^{\circ}X$  and  $X^{\circ}$ . A marking is a vector  $M : P \to \mathbb{N}$  that assigns to each place of a P/T net a non-negative integer number of tokens, represented by black dots. M(p) is the marking of place p.

A net system  $\langle N; M_0 \rangle$  is a net N with an initial marking  $M_0$ . A transition t is marking enabled at M if  $M \geq Pre(\cdot, t)$ . A transition t enabled at M may fire yielding the marking  $M' = M + C(\cdot, t)$ . We write  $M[\sigma > to$  denote that the sequence of transitions  $\sigma$  is enabled at M, and we write  $M[\sigma > M'$  to denote that the firm of  $\sigma$  yields M'. A marking M is reachable in  $\langle N; M_0 \rangle$  iff there exists a firm sequence  $\sigma$  such that  $M_0[\sigma > M$ .

The set of all sequences that are enabled at the initial marking  $M_0$  is denoted  $L(N, M_0)$  i.e.,  $L(N, M_0) = \{\sigma \in T^* | M_0[\sigma > \}$  with  $T^*$  the Kleene closure of set T i.e. the set of all firin sequences of elements of T of arbitrary length, including the empty sequence  $\lambda$ . The notation  $\sigma'\sigma$  will correspond to the firin sequence  $\sigma'$  followed by firin sequence  $\sigma$ , i.e., the concatenation operation;  $\sigma'$  is the prefi of firin sequence  $\sigma'\sigma$ .

The set of all markings reachable from  $M_0$  define the reachability set of  $\langle N; M_0 \rangle$  and is denoted  $R(N, M_0)$ .

Given a net N = (P, T, Pre, Post) and a subset  $T_s \subseteq T$ , the  $T_s$ -induced subnet of N is the net  $N_s = (P, T_s, Pre_s, Post_s)$  where  $Pre_s$  and  $Post_s$  are the restrictions of Pre and Post to  $T_s$ . So, the net  $N_s$  is obtained from N by removing all transitions in  $T \setminus T_s$ , it is denoted also by  $N_s \angle T_s N$ .

#### 3.2. Labels mapping

A labels mapping  $\mathcal{LM}$  is associated to each transition of the net considered as follows

$$\mathcal{LM}: T \to \Omega \bigcup \{\epsilon\},\$$

with  $\Omega$  a finit alphabet and  $\epsilon$  the empty string.

In the proposed approach, the set of transitions is partitioned into two sets: observable transitions whose firin can be detected by an external observer, denoted as  $T_o$  and unobservable transitions whose firin cannot be detected, denoted as  $T_u$  with  $T = T_o \cup T_u$  and  $T_o \cap T_u = \emptyset$ .

More precisely, the following stands:

- $T_u = \{t \in T | \mathcal{LM}(t) = \epsilon\}$ , transitions in  $T_u$  are also called silent,

- $T_o = \{t \in T | \mathcal{LM}(t) \neq \epsilon\}$  (i.e.,  $T_o$  is the set of transitions labeled with a symbol in  $\Omega$ ).

In the proposed approach, the same label  $\zeta \in \Omega$  can be shared by several transitions, i.e., two transitions  $t_i, t_j$ with  $t_i \neq t_j$  will be called indistinguishable if:

$$\mathcal{LM}(t_i) = \mathcal{LM}(t_j) = \zeta.$$

The extension of the label mapping can be realized over sequences,  $\mathcal{LM}: T^* \to \Omega^*$ , recursively as follows:

- 1.  $\mathcal{LM}(t_i) = \zeta \in \Omega \text{ if } t_i \in T_o,$

- 2.  $\mathcal{LM}(t_i) = \epsilon \text{ if } t_i \in T_u,$

- 3. Let  $\sigma \in T^*$  and  $t_i \in T$  then  $\mathcal{LM}(\sigma t_i) = \mathcal{LM}(\sigma)\mathcal{LM}(t_i)$ ,

- 4.  $\mathcal{LM}(\lambda) = \epsilon$  where  $\lambda$  is the empty sequence.

#### 3.3. P-time Petri Nets

**Definitio 1** The formal definitio of a P-TPN (Khansa et al. (1996)) is given by a pair  $\langle N; I \rangle$  where:

- *N* is a marked Place/Transition net (a *P*/*T* net system augmented with a marking)

- $P \to (\mathbb{Q}^+ \cup \{0\}) \times (\mathbb{Q}^+ \cup \{\infty\}),$

- $p_i \rightarrow I(p_i) = [a_i, b_i]$  with  $0 \le a_i \le b_i$

With:

- P: the set of places of the net N,

- $\mathbb{Q}^+$ : the set of positive rational numbers,

- $I_i$  define the static interval of the operation duration of a token in a place  $p_i$ .

A token in place  $p_i$  will be considered in the enabledness of the output transitions of this place if it has stayed for  $a_i$  time units at least and  $b_i$  at the most. Consequently, the token must leave  $p_i$ , at the latest, when its operation duration becomes  $b_i$ . After this duration  $b_i$ , the token will be "dead" and will no longer be considered in the enabledness of the transitions. According to the strong firin mode, a transition in a P-TPN, is forced to fir unless it is disabled by the firin of another conflictin transition. Let consider  $\alpha_i$  the clock associated with the token denoted  $i \in TK$  of the P-TPN (*TK* being the set of tokens of the P-TPN considered). v is a valuation of the system, i.e., a mapping associating to each token i of the P-TPN, an element of  $(\mathbb{R}_{\geq 0})$ ,  $v_i$ , representing the time elapsed since the token i has been created (i.e., the valuation of the clock  $\alpha_i$ ). So,  $v \in (\mathbb{R}_{\geq 0})^{TK}$  with the notation  $A^X$  representing the set of mappings from X to  $A. \overline{0}$  is the initial valuation with  $\forall i, \overline{0}_i = 0$

The semantics of a P-TPN can be define as a Timed Transition System (TTS). A state of the TTS is a couple s = (M, v) where M is a marking and v a valuation of the system.

**Definitio 2** The semantics of a P-TPN  $\langle N; I \rangle$  is define by the Timed Transition System  $S_N = (Q, \{q_0\}, \Sigma, \longrightarrow)$ :

- $I. \ \mathcal{Q} = \mathbb{N}^P \times (\mathbb{Q}_{\geq 0})^{TK}$

- 2.  $q_0 = (M_0, \overline{0})$

- 3.  $\Sigma = T$

- 4.  $\longrightarrow \in \mathcal{Q} \times (\Sigma \cup \mathbb{Q}_{\geq 0}) \times \mathcal{Q}$

- *The continuous transition is define*  $\forall d \in \mathbb{R}_{>0}$  *by:*

$$(M, \upsilon) \stackrel{d}{\to} (M, \upsilon') iff \begin{cases} \upsilon' = \upsilon + d. \\ \forall \text{ token } k \text{ in } p_s \Rightarrow \upsilon'_k \leq b_s. \end{cases}$$

• The discrete transition is define  $\forall t_i \in T$  by:

$(M, \upsilon) \xrightarrow{t_i} (M', \upsilon')$  iff:

$$\begin{array}{l} M \geq^{\circ} t_{i}. \\ \forall \ token \ k \ in \ p_{l}, \upsilon_{k} \leq b_{l}. \\ \forall \ p_{s} \in^{\circ} t_{i}, \forall \ token \ k \ in \ p_{s} \ involved \ in \ t_{i} \ 's \ firin \ : \\ \bigcap_{k} [max(0, a_{s} - \upsilon_{k}), (b_{s} - \upsilon_{k})] \neq \emptyset. \\ M' = M -^{\circ} t_{i} + t_{i}^{\circ}. \\ \forall \ token \ r, \ \upsilon_{r}' = \begin{cases} 0 \ if \ created \ by \ t_{i}. \\ \upsilon_{r} \ otherwise. \end{cases}$$

The dynamic evolution of a P-TPN depends on the timing situation of each token. Indeed, each token will be associated with a potential firin interval (or dynamic interval) which can be different from its static one. For instance, consider place  $p_i$  with static interval  $[a_i, b_i]$ , let a token arrive in place  $p_i$  at absolute time  $\tau$ . At  $\tau$  its potential firin interval will correspond to  $[a_i, b_i]$ . At time  $\tau + c$  with  $c \leq b_i$  the dynamic interval of the considered token will become  $[max(a_i - c, 0), b_i - c]$ . It can be noticed that a token is considered as dead when its dynamic interval becomes [0, 0].

**Definitio 3** *A P*-time labeled Petri net (P-TLPN on short) over an alphabet  $\Omega$  *is a triple*  $\langle N, I, \mathcal{LM} \rangle$  *where*  $\langle N, I \rangle$  *is a P-TPN and*  $\mathcal{LM} : T \to \Omega \bigcup \{\epsilon\}$  *is a labeling function.*

Finally, given a sequence of labels (a word)  $\omega \in \Omega^*$ , it is denoted by  $\omega^k$  the  $k^{th}$  element in  $\omega$  and the number of elements of  $\omega$  is denoted by  $|\omega|$ . For  $a \in \Omega$ , we write  $a \in \omega$  if there exists  $k \ge 1$  such that  $\omega^k = a$  (i.e., a is an element of the word  $\omega$ ).

Furthermore, let  $\omega_1, \omega_2, \ldots, \omega_n$  be *n* sequences of labels (i.e.,  $w_i \in \Omega^*, 1 \le i \le n$ ), the notation  $\omega = \omega_1 \omega_2 \ldots \omega_n$ will be the concatenation of  $\omega_1, \omega_2, \ldots, \omega_n$ .

The next section recalls the procedure (Bonhomme (2015)) to construct the state observer.

#### 4. ESTIMATION PROCEDURE

The goal of the observer is to give the current state estimate of the system based on the information of the observed traces. The state of the observer will consist in a set of states the model can be in after a label observation.

The following set will be associated to any observed word  $\omega$  (i.e., the observed labels sequence):

•  $\mathcal{L}(\omega)$  is the set containing all sequences of transitions that are consistent with  $\omega$ , i.e., the set of all possible firin sequences that produce observation  $\omega$ .

In general, if  $\omega$  is an observed word, the associated firin sequence  $\sigma \in \mathcal{LM}^{-1}(\omega)$  is not necessarily fireable on the net as some unobservable transitions should be interleaved to obtain a fireable sequence that produce  $\omega$ .

**Definitio** 4 Let N be a P-TLPN with  $T = T_o \cup T_u$ . The following operator is defined

- The projection over  $T_o$  is  $P_o: T^* \to T_o^*$  define as: -  $P_o(\lambda) = \lambda$ ,

- for all  $\sigma \in T^*$  and  $t \in T$ ,  $P_o(\sigma t) = P_o(\sigma)t$  if  $t \in T_o$  and  $P_o(\sigma t) = P_o(\sigma)$  otherwise (with  $\lambda$  representing the empty sequence).

Given a sequence  $\sigma \in L(N, M_0)$ ,  $\omega = \mathcal{LM}(P_o(\sigma))$  denotes the corresponding observed word.

**Definitio** 5 Let N be a P-TLPN with  $T = T_o \cup T_u$  and  $\omega \in \Omega^*$  be an observed word.  $\mathcal{L}(\omega)$  is define as:

$$\mathcal{L}(\omega) = P_o^{-1}(\mathcal{L}\mathcal{M}^{-1}(\omega)) \cap L(N, M_0) = \{\sigma \in L(N, M_0) | \mathcal{L}\mathcal{M}(P_o(\sigma)) = \omega\},\$$

*i.e.*, the set of firin sequences consistent with  $\omega \in \Omega^{\star}$ .

**Definitio** 6 Let N be a P-TLPN with  $T = T_o \cup T_u$  and  $\omega \in \Omega^*$  be an observed word.  $C(\omega)$  is define as:

$\mathcal{C}(\omega) = \{ M \in R(N, M_0) | \exists \sigma \in \mathcal{L}(\omega) : M_0[\sigma > M \},\$

*i.e., the set of markings consistent with*  $\omega$ *.*

So, being given an observed word  $\omega$ ,  $\mathcal{L}(\omega)$  is the set of sequences that may have fire while  $\mathcal{C}(\omega)$  is the set of markings in which the system may actually be.

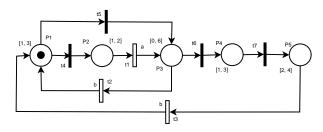

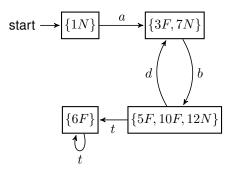

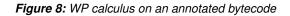

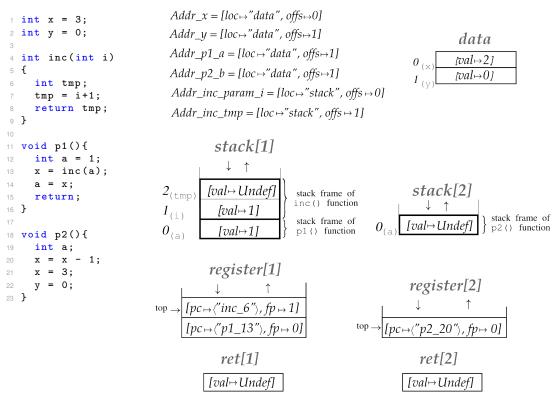

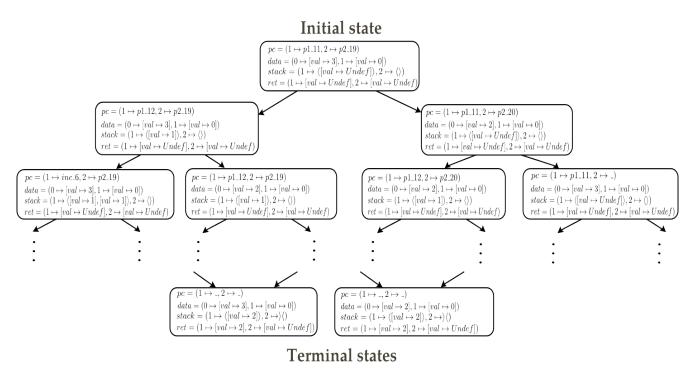

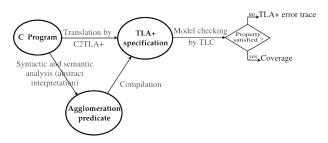

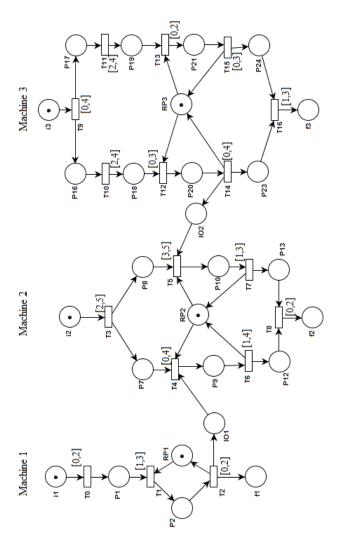

Figure 1: P-TLPN model.

Let consider the P-TLPN of Figure 1 with  $T_u = \{t_4, t_5, t_6, t_7\}, T_o = \{t_1, t_2, t_3\}, \Omega = \{a, b\}$ . It holds  $\mathcal{LM}(t_1) = a, \mathcal{LM}(t_2) = \mathcal{LM}(t_3) = b$  (transitions  $t_2$  and  $t_3$  are indistinguishable) and  $\mathcal{LM}(t_i) = \epsilon, \forall t_i \in T_u$ .

If the observed word is  $\omega = ab$  then  $\mathcal{LM}^{-1}(\omega) = \{t_1t_2, t_1t_3\}$  and  $\mathcal{L}(\omega) = \{t_4t_1t_2, t_4t_1t_6t_7t_3\}$  and  $\mathcal{C}(\omega) = [10000]$ .

**Definitio** 7 Let N be a P-TLPN with  $T = T_o \cup T_u$ , the unobservable reachability mapping UR, which enables to fin the markings reachable from a given marking  $M_i$ , following the firin of all unobservable sequences is define as:

$$\mathcal{UR} : \mathbb{N}^m \to 2^{\mathrm{rs}} ,$$

$$M_i \longrightarrow \mathcal{UR}(M_i)$$

$$\{M_i \in \mathbb{N}^m | \exists \sigma_u \in T^*_u, M_i [\sigma_u > M_i] \},$$

with  $2^{\mathbb{N}^m}$  the power set of the markings of the PN considered.

#### 4.1. State observer

**T**. **T** 2000

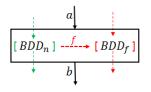

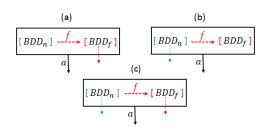

Let  $N_i$  and  $N_j$  be two nodes of the graphical representation of the state observer (associated respectively to the states  $y_i$  and  $y_j$  of the observer) such that it exists a directed arc linking  $N_i$  to  $N_j$  ( $N_i \rightarrow N_j$ , i.e.,  $N_i$  is a predecessor of  $N_j$ ) labeled with  $a_k$  with  $a_k \in \Omega$  as illustrated on Figure2.

Figure 2: nodes of the state observer.

**Definitio 8** The state observer for the partially observable P-TLPN N with initial marking  $M_0$  and  $T = T_o \cup T_u$ is define by the 5-tuple  $(Y_{so}, E_{so}, f_{so}, y_0, \varsigma_{so})$  where:

- $Y_{so}$  is the set of states of the state observer,

- $E_{so} = \Omega$  is the set of labels (associated to the observable events),

- $\varsigma_{so}: Y_{so} \to 2^{R(N,M_0)}$  is a function associating to each state  $y_{so} \in Y_{so}$  a set of reachable markings,

- $y_0$  is the initial state of the state observer and  $\varsigma_{so}(y_0) = SEM(N_0) \cup SSM(N_0)$ ,

- $f_{so}: Y_{so} \times E_{so}^{\star} \to Y_{so}$  is the transition function define as: for  $y_l \in Y_{so}$  a state of the observer and  $\omega \in E_{so}^{\star}$  a string of observable labels  $f_{so}(y_0, \omega) = y_l$  if  $\varsigma_{so}(y_l) \notin \emptyset$  where  $\varsigma_{so}(y_l) =$  $\left\{ M_l: M_0 \xrightarrow{\tau} M_l \wedge \mathcal{LM}(P_o(\tau)) = \omega \right\} =$  $SEM(N_l) \cup SSM(N_l).$

With the two sets SSM and SEM define as follows:

**Definitio** 9 Sets SSM and SEM

•  $SEM(N_j)$ , the Set of Entry Markings of  $N_j$ ,

$$SEM(N_j) = \{M_s \in N_j | \exists M_u \in N_i, t_k \in T_o, \\ a_k \in \Omega, \mathcal{LM}(t_k) = a_k : M_u[t_k > M_s\}$$

•  $SSM(N_j)$ , the Set of Shadow Markings of  $N_j$ ,

$$SSM(N_j) = \{ M_s \in N_j | \exists M_u \in SEM(N_j), \\ \sigma_u \in T_u^\star : M_u [\sigma_u > M_s \} \}$$

or equivalently,  $SSM(N_i) = \mathcal{UR}(SEM(N_i))$ .

Intuitively, for a given node  $N_s$  of the state observer, after the observation of the word  $\omega$ , the set  $SEM(N_s) \cup SSM(N_s)$  represents the set of markings that are consistent with the current observed word (i.e.,  $C(\omega)$ ). The other nodes can be computed recursively as explained in the following.

- 1. The state observer starts in the initial state  $y_0$ and its associated initial node  $N_0$  is composed of  $SEM(N_0) = \{M_0\}$  and  $SSM(N_0) = U\mathcal{R}(M_0)$ .

- 2. as soon as a label  $a_k$  (associated with an observable transition  $t_k \in T_o$ ) is observed a new state  $y_l$  of the observer is calculated yielding a new node  $N_l$ :

- the set of entry markings of node  $N_l$  is obtained by investigating the set of markings resulting from the firin of transition  $t_k$ starting from any marking  $(SEM \cup SSM)$  of  $N_0$ ,

- the set of shadow markings of  $N_l$  corresponds to the set of markings obtained by the firin of all unobservable sequences of transitions starting from any entry marking of  $N_l$ ,

3. return to 2 with the newly calculated state as the initial state.

**Definitio 10** Let  $N_i$  and  $N_j$  be two nodes of the state observer;  $N_i$  and  $N_j$  are said to be equivalent  $(N_i \Leftrightarrow N_j)$  if and only if:

$$SEM(N_i) = SEM(N_i)$$

and  $SSM(N_i) = SSM(N_i)$ .

**Proposition 1** Two nodes  $N_i$  and  $N_j$  of the state observer will be equivalent if and only if, the following holds:

$SEM(N_i) = SEM(N_j).$

**Definitio 11** Given a marking  $M_i \in R(N, M_0)$  and a transition  $t_f \in T_o$  (associated with a label  $l_f \in \Omega$ , i.e.,  $\mathcal{LM}(t_f) = l_f$ ), the set of candidate sequences denoted  $CS(M_i, t_f)$  is the set of firin sequences, composed of the unique fina observable transition  $t_f$ , which can occur from  $M_i$ , i.e.:

$$CS(M_i, t_f) = \{ s.t_f | s \in T_u^* \cup \lambda, t_f \in T_o : M_i[s.t_f > \}.$$

With respect to the timing constraints to be satisfied candidate sequences can be in the state possible or impossible.

As  $N_u \angle_{T_u} N$  (i.e., the Petri net induced by the set of unobservable transitions) is not Zeno by assumption, it is ensured that the time is diverging with regard to the length of the firin sequences, thus, the set of candidate sequences from a marking is necessarily finit (at the instant of observation) and it can be investigated. The following section addresses the schedulability analysis (Bonhomme (2013b)) of an occurrence sequence (i.e., a procedure verifying if the considered firin sequence can occur without any violation of timing constraints) and its application to the estimation problem.

# 5. SCHEDULABILITY ANALYSIS AND ESTIMATION

Let  $\sigma = t_a t_b t_c \dots t_q$  be a firin sequence of length s(denoted  $|\sigma| = s$ ). The  $j^{th}$  fire transition of  $\sigma$  will be associated with the  $j^{th}$  firin instant (Bonhomme (2013a)). A variable  $x_i$  will represent the elapsed time between the  $(i-1)^{th}$  firin instant and the  $i^{th}$  one (with  $x_0 = 0$ ).

For instance on Figure 3,  $(x_2 + x_3)$  is the time elapsed between the firs firin instant (associated with transition  $t_a$ ) and the third one (transition  $t_c$ ).

Figure 3: Firing instants.

In a P-TPN, the sojourn time (i.e., the amount of time that a token has been waiting in a place) is counted up as soon as the token has been dropped in the place as seen previously. To compute the firin instants, this approach requires that a token is identifie by three parameters: the place that contains it, the information of its creation instant and of its consumption one.

Function TOK is define with this purpose assuming that a FIFO queuing policy in the net is used in the sequel:

$$TOK: \mathbb{N} \times (\mathbb{N} \setminus \{0\}) \times T^* \to \wp(P)),$$

$TOK(j, n, \sigma) = \{p \in P | p \text{ contains a token created by the } j^{th} \text{ firm instant and consumed by the } n^{th} \text{ one in firm sequence } \sigma\}.$

With  $\wp(P)$  the set of subsets of P (also noted  $2^P$ ).

When it is clear from the context  $\sigma$  will be omitted in the notation of TOK(.).

When the weight of the P-TPN arcs is element of  $\mathbb{N}$ , TOK(j, n) is a multi-set. For the sake of simplicity, only ordinary P-TPN are considered (the arcs weight are element of  $\{0, 1\}$ ).

Tokens, with the same creation instant, located in different places and involved in the same transition firin may mutually constrained their sojourn time, the following quantities, Dsmin and Dsmax, are introduced in order to evaluate the contribution of these tokens. So, Dsminrepresents their availability in order to participate to this firin and similarly, Dsmax expresses the fact that they all must be prevented from dying (with  $[a_i, b_i]$  the static interval associated with the place  $p_i$ ).

$$Dsmin(j, n) = \begin{cases} \max(a_i), \ i \mid p_i \in TOK(j, n) \\ \text{else 0 if } TOK(j, n) = \emptyset \end{cases},$$

$$Dsmax(j, n) = \begin{cases} \min(b_i), \ i \mid p_i \in TOK(j, n) \\ \text{else } + \infty \text{ if } TOK(j, n) = \emptyset \end{cases}.$$

The definitio of the following set SEN(q), allowing to determine the creation instants of tokens involved in the  $q^{th}$  firin instant, is also necessary:

$$SEN(q) = \{u | TOK(u, q) \subset (\circ t_q)\}$$

To express more simply the obtained results, the definitio of the following coefficient is required:

$$\begin{aligned} c_{uq} &= \left\{ \begin{array}{ll} Dsmin(u,q) & \text{if } u \in SEN(q) \\ 0 & \text{else} \end{array} \right., \\ d_{jk} &= \left\{ \begin{array}{ll} Dsmax(j,k) & \text{if } TOK(j,k) \neq \emptyset \\ +\infty & \text{else} \end{array} \right. \end{aligned}$$

With,  $\forall (j,k) \in [0, q-1] \times [1,q], j \notin SEN(q)$  and  $k \neq q$ , then  $c_{jk} = 0$ , and  $\forall k \in [0,q], x_k \geq 0$ .

The following proposition is finall obtained:

**Proposition 2** A sequence of transitions  $\sigma = t_1 t_2 \dots t_q$ is schedulable (i.e., it may be fi ed respectively at firin instants  $1, 2, \dots, q$ ) if and only if there exist  $x_1 \ge 0$ ,  $x_2 \ge 0, \dots, x_q \ge 0$  such that:

$$c_{0k} \leq x_1 \leq d_{0k}, k = 1, \dots, n$$

$$\max_{\substack{k=2,\dots,n \\ j=0,\dots,q-1 \\ k=q,\dots,n}} (c_{0k}, c_{1k} + x_1) \leq x_1 + x_2 \leq \min_{\substack{k=2,\dots,n \\ s=0}} (d_{0k}, d_{1k} + x_1)$$

$$\dots$$

In the sequel this system will be denoted as  $S_{\sigma}(q)$  or simply  $S_{\sigma}$  when it is clear from the context.

**Definitio 12** The firin space at the  $q^{th}$  firin instant, associated with a firin sequence  $\sigma$ , denoted by  $\mathcal{FS}_{\sigma}(q)$ is the set of non negative vectors  $(x_1, ..., x_q)$  such that the fi st, the second, ... and the  $q^{th}$  firin conditions are satisfied Thus, a firin sequence  $\sigma = t_1 t_2 ... t_q$ is schedulable if and only if its associated firin space  $\mathcal{FS}_{\sigma}(q)$  is non-empty.

Thanks to this characterization of a firin sequence, the Zenoness property can be checked by evaluating the minimal duration of the circuit of unobservable transitions under consideration (for instance, by minimizing the sum of the  $x_i$  associated with the considered transitions).

**Definitio 13** A P-TLPN  $N_r$  firin schedule, will be a sequence of ordered pairs  $(t_i, \sum_{k=0}^{i} x_k)$ ; transition  $t_i$  fi able at time  $(\sum_{k=0}^{i} x_k)$ , obtained from the state reached by starting from  $N_r$  initial state and firin the transitions  $t_j$ ,  $1 \le j < i$ , in the schedule at the given times.

Finally, as in (Basile et al. (2015)), let denote:

$\omega_t = ((a_1, \tau_1), (a_2, \tau_2) \dots (a_n, \tau_n)) \in (\Omega \times \mathbb{Q}^+)^*,$

a time-label sequence (TLS), i.e., a sequence of pairs (observed label-time instant).

Indeed, in the considered sequence, label  $a_i$  is observed at absolute time  $\tau_i$   $(i \ge 1)$  and  $\tau_1 \le \tau_2 \ldots \le \tau_n$ .

Now all the required material for the proposed method is given, the principle is presented as follows:

- starting from the initial state, once a label a<sub>f</sub> will be observed at the absolute time τ<sub>f</sub>,

- the set of associated observable event  $T_{a_f} = \{t \in T_o | \mathcal{LM}(t) = a_f\}$  will be evaluated,

- then,  $\forall t_f \in T_{a_f}$  the set of feasible candidate sequences  $CS(M_0, t_f)$  will be computed,

- a switch from node  $N_0$  to node  $N_f$  (created by the observation of label  $a_f$ ) is realized in the state observer,

- for each σ<sub>f</sub> ∈ CS(M<sub>0</sub>, t<sub>f</sub>) (with P<sub>o</sub>(σ<sub>f</sub>) = t<sub>f</sub>) the associated linear system S<sub>σ<sub>f</sub></sub> will be constructed,

- and each σ<sub>f</sub> will be checked for schedulability with the following additional constraint:

$$\sum_{i=0}^{|\sigma_f|} x_i = \tau_f$$

Thanks to these considerations it is ensured that sequence  $\sigma_f$  is schedulable and the firin of  $t_f$  occurs at  $\tau_f$ . Once a firin sequence is proved to be possible the set of markings the system can be in is then determined.

Let denote by  $FEAS(N_0, t_f)$  the set of schedulable firin sequences from node  $N_0$  ending with the unique observable transition  $t_f$  (it is a subset of the set of candidate sequences).

$$FEAS(N_0, t_f) = \{ \sigma \in CS(M_0, t_f) | \mathcal{FS}_{\sigma}(|\sigma|)$$

augmented with  $\sum_{i=0}^{|\sigma|} x_i = \tau_f$  is non-empty  $\}$ .

Furthermore, based on the knowledge of the schedulable candidate firin sequences only a subset of the set of entry markings of node  $N_f$  (resulting from the firin of transition  $t_f$ ), denoted  $SEM'(N_f)$ , will be considered for the next step.

It holds:

$$SEM'(N_f) = \{ M \in SEM(N_f) | M_0[\sigma > M, \\ \sigma \in FEAS(N_0, t_f) \}.$$

With  $SEM'(N_f) \subseteq SEM(N_f)$ .

Afterwards, if another label  $a_x$  is observed at absolute time  $\tau_x$  then:

- The set of associated observable event  $T_{a_x} = \{t \in T_o | \mathcal{LM}(t) = a_x\}$  will be evaluated,

- then,  $\forall t_x \in T_{a_x}$  the set of feasible candidate sequences  $CS(M_i, t_x)$  will be computed with  $M_i \in SEM'(N_f)$ ,

- a switch from node  $N_f$  to node  $N_x$  is realized in the state observer,

- for each feasible firin sequence (on the underlying untimed PN)  $\sigma'_f \sigma_x$  (i.e.,  $M_0[\sigma'_f \sigma_x >)$  with  $\sigma_x \in CS(M_i, t_x)$  and  $\sigma'_f \in FEAS(N_0, t_f)$  the associated linear system  $S_{\sigma'_f \sigma_x}$  will be constructed.

It is recalled that  $\sigma'_f$  is a schedulable firin sequence determined in the previous step with label  $a_f$  observed at  $\tau_f$  and  $P_o(\sigma'_f \sigma_x) = t_f t_x$ .

• each previously determined  $\sigma'_f \sigma_x$  will be checked for schedulability with the following additional constraint:

$$\sum_{i=0}^{|\sigma'_f|+|\sigma_x|} x_i = \tau_x$$

ensuring that the firin of  $t_x$  occurs at  $\tau_x$ .

And so on, the same method is iteratively applied with respect to the current observation.

So, more formally the following principle is obtained: let  $\omega_{obs}$  be an observed word (i.e., a sequence of labels  $\omega_{obs} = a_1 a_2 a_3 \dots a_i a_{i+1} \dots \in \Omega^*$ ) and let  $N_i$   $(i \ge 1)$ be the node of the associated state observer obtained after the observation of label  $a_i \in \omega_{obs}$  detected at absolute time  $\tau_i$ , as illustrated on the following figur (Figure 4).

Figure 4: Observable sequence.

The associated sets FEAS and SEM' are computed as follows:

Let

$$t_1 \in T_{a_1} = \{t \in T_o | \mathcal{LM}(t) = a_1\},\$$

$FEAS(N_0, t_1) = \{\sigma \in CS(M_0, t_1) | \mathcal{FS}_{\sigma}(|\sigma|) \text{ augmented}$

with  $\sum_{k=0}^{|\sigma|} x_k = \tau_1 \text{ is non-empty} \}.$

$$\begin{split} SEM'(N_0) &= SEM(N_0) = \{M_0\} \text{ and} \\ SEM'(N_1) &= \{M \in SEM(N_1) | M_0[\sigma > M, \\ \sigma \in FEAS(N_0, t_1)\}. \end{split}$$

$\forall i > 0,$

Let  $\mathcal{LM}(t_{i+1}) = a_{i+1}$ ,

$FEAS(N_i, t_{i+1}) = \{ \sigma \in CS(M_b, t_{i+1}) | M_b \in SEM'(N_i),$

$$\begin{split} & M_0[\varpi >, \mathcal{FS}_{\varpi}(|\varpi|) \text{ augmented with} \\ & \sum_{k=0}^{|\varpi|} x_k = \tau_{i+1} \text{ is non-empty} \Big\}. \end{split}$$

With firin sequence  $\varpi = \sigma_1 \sigma_2 \dots \sigma_i \sigma$  where  $\sigma_s \in FEAS(N_{s-1}, t_s), s \in \{1, \dots, i\}$  and  $P_o(\varpi) = t_1 t_2 t_3 \dots t_i t_{i+1}$ .

More precisely:

$$P_{o}(\sigma_{j}) = t_{j}, j \in \{1, \dots, i\} \text{ with } \mathcal{LM}(t_{j}) = a_{j}.$$

$$SEM'(N_{i+1}) = \{M \in SEM(N_{i+1}) | M_{k}[\sigma > M,$$

$$\sigma \in FEAS(N_{i}, t_{i+1}), M_{k} \in SEM(N_{i})\}.$$

$SEM'(N_i)$  is the set of entry markings of node  $N_i$  resulting from the firin of schedulable firin sequences with respect to the current observation.

Roughly speaking,  $FEAS(N_i, t_k)$  is the set of candidate sequences of node  $N_i$  ending with  $t_k$  and which

can be completed by schedulable sub-sequences into a schedulable firin sequence starting from the initial marking of the P-TLPN considered.

So, by this way it is ensured that the feasible firin sequences associated with the observed timelabel sequence  $((a_1, \tau_1), (a_2, \tau_2) \dots (a_{i+1}, \tau_{i+1}))$  are effectively computed.

In the next section, addressing the fault diagnosis problem of a P-TLPN system, this set will be used to evaluate the state diagnosis associated with an observed TLS.

#### 6. FAULT DIAGNOSIS

The set of unobservable transitions is partitioned into two subsets,  $T_u = T_f \cup T_{reg}$  where the set  $T_f$  includes all the fault transitions (modeling anomalous or faulty behavior) while  $T_{reg}$  includes all unobservable transitions which correspond to regular events. Furthermore, the set  $T_f$  is partitioned into r different subsets  $T_f^i$ , where  $i = 1, \ldots, r$ , that models the different fault classes.

**Definitio** 14 Let  $\langle N; M_0 \rangle$  be a net system with labeling function  $\mathcal{LM} : T \rightarrow \Omega \bigcup \{\epsilon\}$ , where N = (P, T, Pre, Post) and  $T = T_o \cup T_u$ . Let consider the TLS  $\omega_t = ((a_1, \tau_1), (a_2, \tau_2) \dots (a_n, \tau_n))$  associated with the state observer of Figure 4.

Let define

$$\sum (M_0, \omega_t) = \{ \sigma \in T^* | M_0[\sigma >, \sigma = \sigma_1 \sigma_2 \dots \sigma_n :$$

$$\mathcal{LM}(\sigma_i) = a_i, i = 1, \dots, n, \sigma_s \in FEAS(N_{s-1}, t_s),$$

$$\mathcal{LM}(t_s) = a_s, s = 1, \dots, n \}$$

Indeed,  $\sigma$  can be viewed as a concatenation of subsequences, namely  $\sigma_i, i \ge 1$ . Each subsequence  $\sigma_i$  is of the form  $s.t_i$  with  $s \in T_u^*$ ,  $\mathcal{LM}(t_i) = a_i$  and absolute firm instant of  $t_i$  is  $\tau_i$ .

So, it holds:

$\sigma_i \in CS(M_b, t_i)$  with  $M_b \in SEM'(N_{i-1})$ .

Definitio 15 A diagnoser is a function

$$\Gamma: [\Omega \times \mathbb{Q}^+]^* \times \left\{ T_f^1, T_f^2, \dots, T_f^r \right\} \to \{N, U, F\}$$

that associates with each observed time-label sequence  $\omega_t$  and each fault class  $T_f^i$ , where  $i = 1, \ldots, r$ , a diagnosis state.

•  $\Gamma(\omega_t, T_f^i) = N$  if  $\forall \sigma \in \sum (M_0, \omega_t)$  and  $\forall t_f \in T_f^i$ , it is  $t_f \notin \sigma$ .

In such a case the  $i^{th}$  fault cannot have occurred, because none of the firin sequences consistent

with the considered observation contains a fault transition of class i.

Γ(ω<sub>t</sub>, T<sup>i</sup><sub>f</sub>) = U if:

∃σ ∈ ∑(M<sub>0</sub>, ω<sub>t</sub>) and t<sub>f</sub> ∈ T<sup>i</sup><sub>f</sub> such that t<sub>f</sub> ∈ σ,

∃σ' ∈ ∑(M<sub>0</sub>, ω<sub>t</sub>) such that ∀t<sub>f</sub> ∈ T<sup>i</sup><sub>f</sub> it is

2.  $\exists \sigma' \in \sum_{f \notin \sigma'} (M_0, \omega_t)$  such that  $\forall t_f \in T_f^i$ , it is  $t_f \notin \sigma'$ .

In such a case a fault transition of class i may have occurred or not, the diagnosis is in this case, uncertain.

•  $\Gamma(\omega_t, T_f^i) = F$  if  $\forall \sigma \in \sum (M_0, \omega_t), \exists t_f \in T_f^i$  such that  $t_f \in \sigma$ .

In such a case the fault of class i must have occurred, because all firable sequences consistent with the considered observation contains at least one fault transition of class i.

Let consider the P-TLPN of Figure1 with  $T_u = \{t_4, t_5, t_6, t_7\}, T_o = \{t_1, t_2, t_3\}, \Omega = \{a, b\}$ . It holds  $\mathcal{LM}(t_1) = a, \mathcal{LM}(t_2) = \mathcal{LM}(t_3) = b$  (transitions  $t_2$  and  $t_3$  are indistinguishable). Furthermore,  $T_f^1 = \{t_5\}$  and  $T_f^2 = \{t_7\}$ , i.e., there are two fault classes.

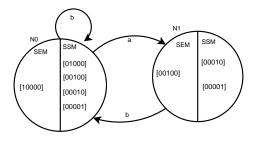

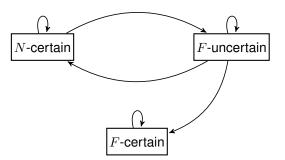

Figure 5: State observer.

The corresponding state observer with two nodes is depicted on Figure 5.

Let consider the following observed TLS  $\omega_t = ((a, 2), (b, 5))$  then:

$\sum_{t_4 t_1 t_6 t_7 t_3.} \sum_{t_4 t_1 t_6 t_7 t_3.} \{\omega_1, \omega_2\} \text{ with } \omega_1 = t_4 t_1 t_2 \text{ and } \omega_2 = t_4 t_1 t_6 t_7 t_3.$

We have (according to the notations of definitio 14):

- $\omega_1 = \sigma_1 \sigma_2$  with  $\sigma_1 = t_4 t_1$  and  $\sigma_2 = t_2$ ,

- $\omega_2 = \sigma_1 \sigma_2$  with  $\sigma_1 = t_4 t_1$  and  $\sigma_2 = t_6 t_7 t_3$ .

The two obtained candidate sequences are feasible with regard to the timing constraints. Indeed, the two associated firin schedules can be, for instance, considered respectively for  $\omega_1$  and  $\omega_2$ :

- $((t_4, 1), (t_1, 2), (t_2, 5)),$

- $((t_4, 1), (t_1, 2), (t_6, 2), (t_7, 3), (t_3, 5)).$

It holds  $t_7 \in T_f^2$  and  $t_7 \in \omega_2$   $(t_7 \notin \omega_1)$ , and  $t_5 \in T_f^1$ ,  $t_5 \notin \omega_1, t_5 \notin \omega_2$ .

So,

$$\Gamma(\omega_t, T_f^1) = N$$

and  $\Gamma(\omega_t, T_f^2) = U$ .

It means, that according to the previous observed time label sequence  $\omega_t$ , it is known for sure that the fault of class 1 (corresponding to fault transition  $t_5$ ) cannot have occurred while fault transition  $t_7 \in T_f^2$  may have occurred (via  $\omega_2$ ).

If the observed TLS corresponds to  $\omega_t = (b, 1)$ , it is easy to verify that  $\sum (M_0, \omega_t) = \{\omega_3\}$  with  $\omega_3 = t_5 t_2$ (the associated firm schedule is  $((t_5, 1), (t_2, 1))$ ) and consequently,  $\Gamma(\omega_t, T_f^1) = F$  and  $\Gamma(\omega_t, T_f^2) = N$  (i.e., a fault of class  $T_f^1$  occurs for sure and a fault of the second class cannot have occurred).

In the next section an illustrative example is presented where the  $T_u$ -induced subnet is cyclic.

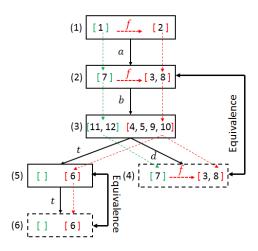

#### 7. ILLUSTRATIVE EXAMPLE

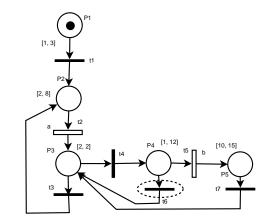

Let consider the P-TLPN of Figure 6 with  $T_o = \{t_2, t_5\}$ ,  $T_u = \{t_1, t_3, t_4, t_6, t_7\}$ ,  $T_f = \{t_6\}$  and  $\mathcal{LM}(t_2) = a$ ,  $\mathcal{LM}(t_5) = b$ . The  $T_u$ -induced subnet contains the cycle  $(p_3 - t_4 - p_4 - t_6 - p_3)$ .

*Figure 6: P*-*TLPN* with a cyclic  $T_u$ -induced subnet.

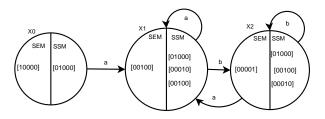

The state observer is depicted on Figure 7, it consists of three nodes  $X_0, X_1$  and  $X_2$ .

Figure 7: State observer of the P-TLPN of Figure 6.

If the observed word is  $\omega = (a, b)$  then the set of possible associated firm sequences is of the form  $t_1t_2t_4(t_6t_4)^*t_5$ with the  $\star$  after the subsequence  $(t_6t_4)$  (derived from the Kleene star operator) indicating that it is allowed to occur from zero time to infinitel . Thanks to the time instant of occurrence of each label the set of feasible associated firin sequences is necessarily finite

For instance if the TLS considered is:

$\omega_t = ((a,3), (b,6))$  then  $\sum (M_0, \omega_t) = \{\omega_1\}$  with  $\omega_1 = t_1 t_2 t_4 t_5$ . The associated firm space  $\mathcal{FS}_{\omega_1}(|\omega_1|)$  augmented with the following constraints:

- $x_1 + x_2 = 3$  (absolute firm instant of transition  $t_2$ ),

- $x_1 + x_2 + x_3 + x_4 = 6$  (absolute firm instant of transition  $t_5$ ),

is non-empty.

It holds:

$\omega_1 = \sigma_1 \sigma_2$  with  $\sigma_1 = t_1 t_2$  and  $\sigma_2 = t_4 t_5$  and an example of firm schedule is:

$\varpi = ((t_1, 1), (t_2, 3), (t_4, 5), (t_5, 6)),$

and it is unique with respect to the static intervals of the P-TLPN places. So, it is easy to see that  $\Gamma(\omega_t, T_f) = N$  and the faulty transition  $t_6$  cannot have occurred.

If the TLS considered is now:  $\omega_t = ((a, 3), (b, 9))$  then  $\Gamma(\omega_t, T_f) = U$ , as the computation of the set  $\sum (M_0, \omega_t)$  leads to the following possible firm schedules (with the same observable projection), one containing the faulty transition and the other one not:

•

$$\varpi_1 = ((t_1, 1), (t_2, 3), (t_4, 5), (t_5, 9)),$$

•  $\varpi_2 = ((t_1, 1), (t_2, 3), (t_4, 5), (\underline{t_6}, 6), (t_4, 8), (t_5, 9)).$

If the TLS considered is now:  $\omega_t = ((a, 3), (a, 14))$ then  $\Gamma(\omega_t, T_f) = F$ . Indeed, the computation of the set  $\sum (M_0, \omega_t)$  leads to the following possible firin schedule containing the faulty transition:

•

$$\varpi_2 = ((t_1, 1), (t_2, 3), (t_4, 5), (\underline{t_6}, 10), (t_3, 12), (t_2, 14)).$$

In this case the faulty transition occurs with certainty thanks to the timing structure of the P-TLPN considered and the occurrence date of the observed labels.

#### 8. CONCLUSION AND PERSPECTIVES

In this paper, a new methodology allowing to analyze the fault diagnosis of systems modeled by P-time labeled Petri nets is developed. It is based on the construction of a function called diagnoser which associates with each observation and each fault class a diagnosis state. This diagnoser is obtained thanks to the synthesis of a state observer which is an automaton allowing to estimate the set of markings in which the system may be, being given a sequence of observed labels.

Furthermore, the considered state observer is computed on the basis of the untimed underlying Petri net of the P-time labeled PN considered. This particularity allows to avoid the combinatorial state space explosion problem usually associated with the consideration of the time factor modeled as time intervals.

Thanks to a schedulability analysis technique, the feasibility of the candidate firin sequences associated with the observed time-label sequence is evaluated via linear programming techniques.

An issue currently being investigated is the extension of the method to test the diagnosability property of P-TLPN systems, i.e., is the fault can be detected within a finit number of steps after its occurrence ?

#### REFERENCES

- Basile, F., M. Cabasino, and C. Seatzu (2015, April). State estimation and fault diagnosis of labeled time petri net systems with unobservable transitions. *Automatic Control, IEEE Transactions on 60*(4), 997–1009.

- Basile, F., M. P. Cabasino, and C. Seatzu (2013). Marking estimation of time Petri nets with unobservable transitions. In *IEEE Emerging Technologies and Factory Automation (ETFA)*, pp. 1–7.

- Berthomieu, B. and M. Diaz (1991, March). Modeling and verificatio of time dependent systems using time petri nets. *IEEE Trans. Softw. Eng.* 17(3), 259–273.

- Bonhomme, P. (2013a). Scheduling and control of realtime systems based on a token player approach. *Journal* of Discrete Event Dynamic Systems 23(2), 197–209.

- Bonhomme, P. (2013b). Towards a new schedulability technique of real-time systems modeled by p-time Petri nets. *International Journal of Advanced Manufacturing Technology* 67(1-4), 759–769.

- Bonhomme, P. (2014). Estimation of p-time labeled petri nets with unobservable transitions. In *Proceedings* of the 2014 IEEE Emerging Technology and Factory Automation, ETFA 2014, Barcelona, Spain, September 16-19, 2014, pp. 1–8.

- Bonhomme, P. (2015). Marking estimation of P-time Petri nets with unobservable transitions. *IEEE Transactions* on Systems, Man, and Cybernetics: Systems 45(3), 508– 518.

- Cabasino, M., A. Giua, and C. Seatzu (2010). Fault detection for discrete event systems using Petri nets with unobservable transitions. *Automatica* 46(9), 1531–1539.

- Cabasino, M. P., A. Giua, and C. Seatzu (2014). Diagnosability of discrete event systems using labeled Petri nets. *IEEE Transactions on Automation Science* and Engineering 11(1), 144–153.

- Cassandras, C. G. and S. Lafortune (2008). *Introduction* to Discrete Event Systems. Springer-Verlag New York, Inc.

- Cassez, F. and S. Tripakis (2008). Fault diagnosis with dynamic observers. In *Discrete Event Systems, 2008. WODES 2008. 9th International Workshop on*, pp. 212–217.

- Giua, A., C. Seatzu, and D. Corona (2007). Marking estimation of Petri nets with silent transitions. *IEEE Transactions on Automatic Control* 52(9), 1695–1699.

- Hadjidj, R., H. Boucheneb, and D. Hadjidj (2007). Zenoness detection and timed model checking for real time systems. In *VECoS'07*, pp. 120–134.

- Khansa, W., J. P. Denat, and S. Collart-Dutilleul (1996). P-time Petri nets for manufacturing systems. In WODES'96, Edinburgh UK, pp. 94–102.

- Lin, F. (1994). Diagnosability of discrete event systems and its applications. *Discrete Event Dynamic Systems* 4(2), 197–212.

- Merlin, P. and D. Faber (1976). Recoverability of communication protocols-implications of a theoretical study. *IEEE Trans. Comm.* 24(9), 381–404.

- Murata, T. (1989). Petri nets, properties, analysis and applications. *Proceedings of the IEEE* 77, 541–580.

- Sampath, M., R. Sengupta, S. Lafortune, K. Sinnamohideen, and D. Teneketzis (1995). Diagnosability of discrete-event systems. *IEEE Transactions on Automatic Control* 40(9), 15551575.

- Wang, X., C. Mahulea, and M. Silva (2013, 07/2013). Fault diagnosis graph of time petri nets. In ECC'13: European Control Conference, Zurich, Switzerland.

- Wang, X., C. Mahulea, and M. Silva (2014). Model checking on fault diagnosis graph. In *12th International* Workshop on Discrete Event Systems, WODES 2014, Cachan, France, May 14-16, 2014., pp. 434–439.

- Zaytoon, J. and S. Lafortune (2013). Overview of fault diagnosis methods for discrete event systems. *Annual Reviews in Control* 37(2), 308 320.

# Combining Enumerative and Symbolic Techniques for Diagnosis of Discrete-Event Systems

Abderraouf Boussif Univ. Lille Nord de France, F-59000 Lille, France IFSTTAR, Cosys/Estas, F-59650 Villenveuve d'Ascq, France FR abderraouf.boussif@ifsttar.fr Mohamed Ghazel Univ. Lille Nord de France, F-59000 Lille, France IFSTTAR, Cosys/Estas, F-59650 Villenveuve d'Ascq, France FR mohamed.ghazel@ifsttar.fr Kais Klai LIPN, CNRS UMR 7030, Univ. Paris 13, Sorbonne Paris Cité,

FR kais.klai@lipn.univ-paris13.fr

In this paper, an efficient approach to verify diagnosability of discrete-event systems is proposed. The approach consists in constructing a hybrid diagnoser based on the symbolic observation graph (SOG), which is a technique that combines symbolic and enumerative representations in order to build a deterministic observer from a partially observed model. The construction of the diagnoser as well as the verification of diagnosability are performed simultaneously on-the-fly, which can considerably reduce the generated state space of the diagnoser and thus the overall running time. Furthermore, the proposed approach provides a heuristic strategy in order to converge fast into the necessary part, of the diagnoser, for analysing diagnosability.

Discrete-Event Systems, Diagnosability Analysis, Symbolic Observer Graph, On-the-Fly Verification.

### 1. INTRODUCTION

In automated monitoring and fault diagnosis of complex dynamic systems, one of the central tasks is to detect and identify the occurrence of failures as early as possible. This task has become an active research area in recent years (Zaytoon and Lafortune 2013). From the theoretical point of view and at a high level of abstraction, Discrete-Event Systems (DESs) are more suitable for performing diagnosis analysis on complex systems (Cassandras and Lafortune 2007).

One of the main issues in diagnosis activity that must be addressed is diagnosability investigation. Analysing diagnosability of a system intends to determine accurately whether any predetermined failure or class of failures can be detected and identified within a finite delay following its occurrence (Sampath et al. 1995).

Diagnosability verification has received considerable attention since the seminal paper by (Sampath et al. 1995), which provides a basic concept and a formal definition of diagnosability analysis and fault diagnosis of DESs that were adopted and further developed later. In this paper, (Sampath et al. 1995), the original definition of diagnosability was introduced in the language context. A systematic method to check diagnosability based on a dedicated deterministic version of the model derived from the original system, a so-called *diagnoser*, was also provided. It consists of a specific observer of the system associated with a labelling function that attributes to each state (or macro-state), in this observer, a label indicating whether the state is reached by a faulty execution or not, i.e. an execution where some particular unobservable events, called *faults*, have occurred or not.

Other automata-based approaches (Jiang et al. 2001; Yoo and Lafortune 2002), aiming to reduce computational complexity have been then proposed. In (Yoo and Lafortune 2002), a polynomial-time algorithm for checking diagnosability based on a structure called *verifier* is adopted. In (Jiang et al. 2001), an algorithm based on the twin plant structure (a parallel composition of the investigated automaton with itself) is proposed. Reformulations of these works in model-checking framework were first proposed in (Cimatti et al. 2003) and extended in (Boussif and Ghazel 2015). The goal is to check

diagnosability property in the same way as to check any safety property.

Furthermore, some works on diagnosability of DESs turned to Petri nets (PNs) formalism, benefiting from the mathematical and graphical representations capability and the well-developed theory underlying PNs (Peterson 1981). (Ushio et al. 1998) extended Sampath's study to systems modelled by PNs with the assumption that some places are observables whereas all of the transitions are unobservable. A diagnoser is constructed from the reachability graph. In (Wen and Li 2005), the authors proposed a sufficient condition for testing diagnosability by checking the structure of T-invariants of a PN. In (Cabasino et al. 2009) the modified basis reachability graph (MBRG) and basis reachability diagnoser (BRD), which provide a compact representation of the reachability graph, were developed. In (Basile et al. 2012), an approach for checking diagnosability by quantifying the finite delay of diagnosability (the so-called Kdiagnosability) was proposed by using the integer linear programming (ILP) technique. A structure called verifier net (VN) was introduced in (Cabasino et al. 2014) to deal with diagnosability for both bounded and unbounded PNs. Recently. (Liu et al. 2014a) has proposed an on-the-fly and incremental diagnosis technique to construct a diagnoser from a bounded PN in order to verify diagnosability and Kdiagnosability properties.

To get a general overview on the literature pertaining to diagnosis of DESs, the reader can refer to the recent survey in (Zaytoon and Lafortune 2013), where theoretical and practical issues, tools and other issues in relation with diagnosis are discussed.

The challenge of analysing diagnosability is the combinatorial explosion problem that appears during the building of the intermediate models (diagnoser, verifier, twin plant, MBRG, etc.). This is due to the high complexity of these constructed models and to the generation of the whole state-space which may have considerable time and memory cost.

To partially overcome this problem, we propose, in this paper, an efficient approach to construct a hybrid diagnoser on-the-fly, in the sense of combining enumerative and symbolic techniques. The contributions of this paper are twofold:

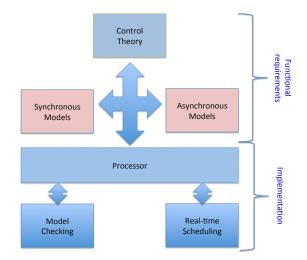

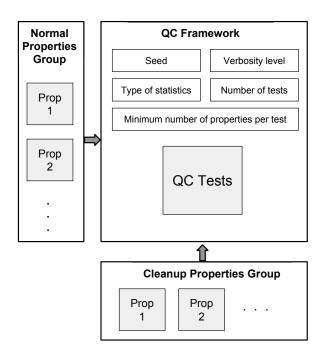

1. We provide a behavioural diagnoser based on the Symbolic Observation Graph (Haddad et al. 2004) which is an efficient binary decision diagram (BDD) based abstraction of the model state space. Thus, macro-states of the diagnoser will be compacted using BDDs while transitions between macro-states are represented by enumerate observable events.

2. We design an appropriate algorithm, for simultaneously constructing the diagnoser and checking diagnosability on-the-fly. Actually, the verification process is stopped (only a part of the diagnoser is built) as soon as the diagnosability is proven to be unsatisfied, which can considerably reduce the generated state space of the diagnoser. Furthermore, the proposed algorithm is endowed with a heuristic strategy in order to converge fast into the necessary part of the diagnoser for diagnosability analysis.

The paper is structured as follows. In Section 2, we introduce the basic background needed to deal with diagnosability and to develop our approach. In Section 3, we recall the notion of diagnosability as well as the original diagnoser approach. Section 4 is devoted to discuss the Symbolic Observation Graph adapted to the context of this paper. In Section 5, the verification approach is sketched out then an on-the-fly algorithm based on the SOG is presented. Section 6 discusses the pertinent existing work in relation with the present work. Finally, conclusion remarks and future research directions are given in Section 7.

# 2. PRELIMINARIES

We first recall some standard notations that will be used in the sequel. Let  $\Sigma$  be a finite alphabet of events (actions). A string is a finite sequence of events in  $\Sigma$ .  $\epsilon$  denotes the empty string. Given a string *s*, the length of *s* is denoted by |s|. The set of all strings formed by events in  $\Sigma$  is denoted by  $\Sigma^*$ . Any subset of  $\Sigma^*$  is called a *language*. Given a string  $s \in L, L/s \triangleq \{t \in \Sigma^* | s.t \in L\}$  is called the *postlanguage* of *L* after *s* and defined as L/s. *L* is said to be *extension-closed* when  $L.\Sigma^* = L$ .

The approach introduced in this paper applies to discrete-events systems modelled by Labelled Transitions Systems (LTSs for short). The formal definition of LTS is as follows.

**Definition 1** *(LTS):* An LTS over  $\Sigma$  is defined by a 4-tuple  $\langle Q, \Sigma, \rightarrow, q_0 \rangle$ , where:

- Q is a finite set of states;

- $\Sigma$  is a finite set of events;

- $\rightarrow \subseteq Q \times \Sigma \times Q$  is the transition relation;

- $q_0 \in Q$  is the initial state.

In the remainder of this section, we consider a given LTS  $G = \langle Q, \Sigma, \rightarrow, q_0 \rangle$ . For  $q, q' \in Q$  and  $\sigma \in \Sigma$ , we denote  $q \xrightarrow{\sigma} q' \triangleq (q, \sigma, q') \in \rightarrow$ .  $q \rightarrow$  means that  $\exists q' \in Q : q \xrightarrow{\sigma} q'$ . If  $s = \sigma_1, \sigma_2, \ldots, \sigma_n$  is a string (sequence of events),  $\bar{s}$  denotes the set of actions occurring in s. Moreover,  $q \xrightarrow{s} q'$  denotes that  $\exists q_1, q_2, \ldots, q_{n-1} \in Q$  such that,  $q \xrightarrow{\sigma_1} q_1 \xrightarrow{\sigma_2} \ldots q_{n-1} \xrightarrow{\sigma_n} q'$ .  $q \xrightarrow{s} q'$  denotes that q' is reachable from q (i.e.  $q \xrightarrow{s} q'$  for some  $s \in \Sigma^*$ ), and  $q \xrightarrow{*}_E q'$  holds if  $\bar{s} \subseteq E$ .

We denote by Enable(q) the set of events  $\sigma$  s.t.  $q \xrightarrow{\sigma}$ , for a set of states  $Q' \subseteq Q$ ,  $Enable_E(Q')$  denote the set of enabled events from the set of states Q', i.e. Enable(Q') denotes  $\bigcup_{q \in Q'} Enable(q)$ .

An execution from the initial state  $q_0$  of an LTS G is a finite sequence of transitions  $\pi = q_0 \xrightarrow{\sigma_1} q_1 \dots \xrightarrow{\sigma_n} q_n$ . The event-trace of  $\pi$ , denoted by  $Tr(\pi)$ , is the sequence of events  $\sigma_1, \dots, \sigma_n, \pi[i]$  stands for the prefix of  $\pi$  truncated at state  $q_i$ , i.e.,  $\pi[i] = q_0 \xrightarrow{\sigma_1} q_1 \dots \xrightarrow{\sigma_i} q_i$  and  $last(\pi)$  represents the last state of  $\pi$ . The set of finite executions of LTS G from the initial state  $q_0$  is denoted by Runs(G). The behaviour of Gis described by its language  $L(G) = \{s \in \Sigma^* | q_0 \xrightarrow{s} \}$ .

As we are interested in diagnosis issues, partial observation plays a central role. In this regard, some events in  $\Sigma$  are observable, i.e. their occurrence can be observed, while the rest are unobservable. Thus, the event set  $\Sigma$  can be partitioned as  $\Sigma = \Sigma_o |+| \Sigma_u$ , where  $\Sigma_o$  denotes the set of observable events and  $\Sigma_u$  the set of unobservable events. To reflect the limitation on observation, we define the projection function  $P: \Sigma^* \to \Sigma_{\alpha}^*$ . In the usual manner,  $P(\sigma) = \sigma$ for  $\sigma \in \Sigma_o$ ;  $P(\sigma) = \epsilon$  for  $\sigma \in \Sigma_u$ , and  $P(s\sigma) =$  $P(s)P(\sigma)$ , where  $s \in \Sigma^*$ ,  $\sigma \in \Sigma$ . Thus, P simply erases the unobservable events in any event-trace. The inverse projection operation  $P_L^{-1}$  is defined by  $P_L^{-1}(y) = \{s \in L(G) : P(s) = y\}$ . Any two executions  $\pi$  and  $\pi'$  are called *indistinguishable* with respect to the projection function P if they can generate the same observed event-trace. With a slight abuse of notation, we write  $P(\pi) = P(\pi')$  if  $\pi$  and  $\pi'$  are indistinguishable.

In the context of fault diagnosis, let  $\Sigma_f \subseteq \Sigma_u$  denote the set of failure events. They are usually represented using unobservable events, since their detection and diagnosis would be trivial if they were observable. We partition the set of failure events into disjoint failure classes  $\Sigma_f = \Sigma_{f_1} \biguplus \Sigma_{f_2} \oiint \cdots \biguplus \Sigma_{f_m}$ , with  $\Sigma_{f_i}$  denotes the failure class  $f_i$ .

### 3. DIAGNOSABILITY ANALYSIS

In this work, only diagnosability analysis of permanent faults is considered. Once a fault has occurred, the system remains irreparably faulty. We assume that the LTS G under consideration satisfies the following two assumptions: