# Development of a JFET model with increased accuracy: measurements of wrangling data, acquisition and model analysis

Viktoriia Hnatushenko<sup>1,2,\*,†</sup>, Anton Guda<sup>1,†</sup>, Andrew Zimoglyad<sup>1,†</sup> and Anna Zhurba<sup>1,†</sup>

#### **Abstract**

Junction gate field - effect transistors have a significant role in the modern electronics. Simulation of the electronic schematics is a crucial part of the modern devices development. At the present time an existent model are used. A drawbacks of the exiting JFET models, with are commonly used during electronic schematics simulation a described. For the tasks of precision simulation the simple approximation functions and switching conditions lead to accuracy loss. A general purpose and specialized hardware and software complex was created to acquire measurement data. This measurement complex gives as possibility to acquire measurement data in automatic and semi-automatic modes. A bulk amount of data about selected JFET species was collected. According to this data a new model was proposed. This model allows us identify parameters in sequence, which significantly decreases the possibility of the identification errors. Proposed model requires more complex calculations to achieve results, and more data to conduct parametric identification. But as the result, new model provides better agreement with experimental data, especially in low-voltage regimes. New model allows us to decrease simulation error level from the 20% to 1-5%. The proposed model provides better qualitative conforming to the experimental data.

# **Keywords**

data acquisition, wrangling data, semiconductor devices simulation, function approximation, automatic measurement.

# 1. Introduction

In modern electronics schematics, junction-gate field-effect transistors (JFETs) are not as commonly used separately as, for example, field-effect transistors with an isolated gate (MOSFETs). On the other hand, JFETs are widely used as part of more complex structures, such as the input stages of operational amplifiers with high input impedance, current sources in measurement equipment, and miscellaneous low-current sensors [1,2]. Low resistance in the "on" state makes these devices applicable in relaxation systems [3]. Since amplifiers with a JFET input have high input impedance, they may be used as microphone preamplifiers for high-quality condenser and electret microphones in smart-home voice assistants, "nanny" cameras, and voice control systems [4]. The same property allows us to implement home security systems based on piezoelectric vibration sensors [5], ion chamber smoke detectors, thin-film gas sensors, and pressure and humidity MEMS sensors for climate control [6]. Some of the even-harmonic mixing properties of the JFET are valuable in audio design [7,8].

<sup>🕩 0000-0001-5304-4144 (</sup>Vik. Hnatushenko), 0000-0003-1139-1580 (A. Guda), 0009-0001-7239-2467 (A. Zimoglyad); 0000-0002-4367-385X (A. Zhurba)

© 2025 Copyright for this paper by its authors. Use permitted under Creative Commons License Attribution 4.0 International (CC BY 4.0).

Dnipro Metallurgical Institute Ukrainian State University of Science and Technologies, Science avenue 4, 49000 Dnipro, Ukraine

<sup>&</sup>lt;sup>2</sup> Institute of Photogrammetry and GeoInformation, Leibniz University, Nienburger Str. 1-4, 30167 Hannover, Germany

<sup>\*</sup>CIAW-2025: Computational Intelligence Application Workshop, September 26-27, 2025, Lviv, Ukraine

<sup>1\*</sup> Corresponding author.

<sup>&</sup>lt;sup>†</sup>These authors contributed equally.

<sup>🔁</sup> vik.v.hnatushenko@ust.edu.ua (Vik. Hnatushenko); atu.guda@gmail.com (A. Guda); azee77871152@gmail.com (A. Zimoglyad); annette.zhurba@gmail.com (A. Zhurba)

The possibility of essential current control without significant current in the control circuit without tending to on/off mode makes these devices preferable in the satellites, small IoT devices and wearable equipment, where power sources have really restricted capabilities. Therefore, creating new models with increased accuracy is an important task in the design of modern electronic devices, especially when limiting power consumption.

# 2. Related work

Obliviously, a formidable amount of models are used with clear success during design and development. And during these processes well-known JFET models are used [9,10,11,12,13]. Some of the models are devoted to the modern SiC, GaN devices [12,14]. Essential efforts was made if the field of physical background justification [10,13,15].

However, most of these models, especially used in the well-known electronic circuits simulation software, like those based on the ng-spice simulation engine [16,17,18,19,20,21], Itspice engine [21,22,23,24-26], demonstrates limited applicability when JFET is used outside common working modes. Moreover, unusual working modes with low current value may be used when the task is to provide sensors current stabilization in a limited power budget, especially in cosmic and autonomous systems.

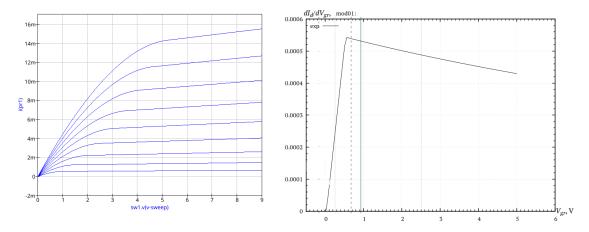

As an example, let's examine  $I_d(V_{gs})$  characteristic and its derivative for the BF-245C JFET. This data was acquired by the ques-s [27] simulation software, which, in turn, uses ngspice engine.

**Figure 1:**  $I_d(V_{gs})$  characteristic and its derivative, obtained via ques-s simulation program.

As we can see, this plot consists of three distinct parts. While the first (cut-off) and the second (quadratic) parts have good confirmation with the real world, the third region, which is represented by the quadratic dependence in this model, not so precisely represents the real device behavior. One of the significant features of the JFET is near to linear current dependence in this range up to break-down. The plot on the fig. 1 shows, that model, used in the ngspice engines, have parabolic characteristic in this area. Moreover, different JFETs demonstrate distinctive behavior at the junction area between send and third parts.

Another essential phenomena, which is not covered by this model, is dependence of the cut-off voltage ( $V_{gs0}$ ) from the drain-source voltage ( $V_{ds}$ ). The existence of this dependence is well-known, but not represented in the existent model.

One of the significant limitations of the existent models is the extremely simplified object representation and boundary conditions. Usually assumed, that channel has a simple form of rectangular thin film. The gate junction is assumed to be a flat one-dimension structure. Real devices now have a more complex structure. Moreover, the realization details are not publicly available. Even with these details assumed to be known, it is required a supercomputer and

elaborated quantum simulation software to achieve the correct result. This approach is not suitable for real electronic schematics simulation, where simple and fast calculated algorithms are required.

# 3. Research objectives

In accordance with the above, the research goals are treated as follows:

- Provide a simple static JFET model, suitable for the electronic schematics simulation and capable to represent more features of the real device. The new model should provide a better match with experimental data, possibly at the expense of increased model complexity.

- Develop a method to identify the parameters of this model, preferable with minimal human interaction. This method must provide model coefficients with minimal human interaction, and, consequently, lower error level.

#### 4. Materials and methods

Development of this class of models is impossible without a bulk amount of measured data. Hand-made measurements are theoretically possible, but error-prone and amount of spent time will be enormous. So, to provide the required amount of experimental data special programmable measurement equipment must be created. We must take into account, that this data is wrangling and subjected to numerous errors.

First of all, we need to determine the measured values and the corresponding ranges. The set of values to measure is limited: drain-source voltage ( $V_{ds}$ ), gate-source voltage ( $V_{gs}$ ) and drain current ( $I_d$ ). Moreover, the voltages under consideration must be not only measured, but controlled in the given ranges.

The ranges of the measured and/or controlled values are defined by the devices under investigation. To provide wide band of parameters, not crossing the borders of available resources, the following set of low-power JFETs was chosen: BF245B [28], J111 [29], J112, MMBF4391 [30]. This set provides an essential range of  $V_{gs0}$  values, slightly different forms of the dependencies under consideration, but the maximum values are limited enough to be measured by the available and designed equipment. The working  $V_{gs}$  range is -10..0 V. The maximum drain current, according to datasheets, is roughly 100 mA. The drain-source voltage is limited to 30 V. This range is not so convenient to control, but the over power limitation does not give us the possibility to use the full voltage range. On the one hand, this fact slightly limits model applicability. On the other hand, this gives us a chance to use already created equipment as a part of the measurement system.

The proposed central part of the measurement system is developed programmable control and measurement system "cube" (fig 2). This system provides both manual and programmable control and measurement of such values: 2 analog output channels with –10..10 V range (12 bit resolution), 4 analog input –9..9 V range (16 bit resolution, high impedance), 8 "slow" digital input channels, 8 "slow" digital output channels, 4 "fast" digital input channels with timer-based measurement capabilities, 4 "fast" digital output channels with PWM, LWM.

Figure 2: Front panel of the "cube" measurement system.

The core of this system is a STM32F407VGT microcontroller. The firmware provides us the possibility not only to manually measure and control required values, but to do this under program control. As the user-visible programming language the C-alike interpreter is used. It was derived from open-source "pico-c" project [31] and adopted to measurement needs. Programs may be loaded both with UART interface and USB flash drive. The results may be stored the same way, not counting the LCD screen.

Taking into account the characteristics above, we can measure both  $V_{gs}$  and  $V_{ds}$  by the "cube" directly via analog input channels. The  $V_{gs}$  value we can control by the analog output channel without extra parts. Unfortunately, the analog output channel is not powerful enough to drive JFETs at full required power. So, an external power supply RD6006P [32] was used to drive  $V_{ds}$ . This decision adds some amount of manual control during measurements, but this amount was acceptable.

To measure the  $I_d$  value, an additional device was required. To measure current on the "high side" across a small (0.1-1 Ohm) shunt resistor without significant errors, a specialized amplifier board with the AD8221 – a precision instrumentation amplifier [33,34] – was developed and used (Fig. 3). A high common-mode rejection ratio (approximately 130 dB) allows us to measure the voltage drop across a shunt resistor on the high side with negligible errors. Measuring current on the low side under these conditions would lead to significant errors in  $V_{gs}$  measurement. After amplification (×99.97), the current signal was measured by an analog input channel. All measurement and control channels were calibrated using a precision SDM3035 multimeter. The calibration results show that in the range of -9 to 9 V, the error does not exceed 0.1% if the thermal conditions are stable. However, outside of this range, the error grows significantly, up to full phase reversal. This can be mainly explained by the limited input range of the TL072 operational amplifier in the input stage of the measurement block. The main source of current measurement error was assumed to be the shunt resistor's thermal instability. For the reasons above, the total measurement error does not exceed 1%. It is worth mentioning that the input stage of the TL072 amplifier is based on an integrated JFET pair, which provides high input impedance and really low non-linear distortions.

Figure 3: Specialized amplifier board with AD8221.

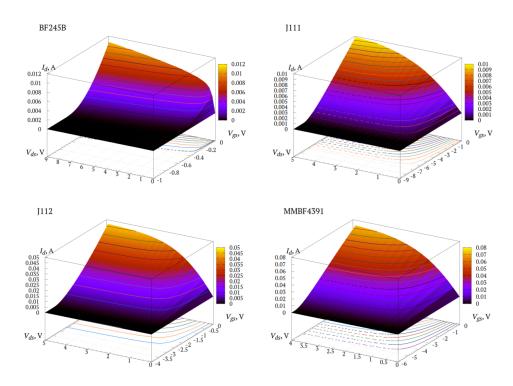

The measurements were conducted using the following procedure. First of all, a sample JFET was connected to the measurement system. Then, under manual control a small amount of data points was acquired. During these tests critical checks like maximum power, junction temperature were conducted. If the results of these tests were not satisfactory, then the voltage ranges were adjusted. Then a program, loaded on the flash drive was used to semi-automatically iterate over  $V_{ds}$  and  $V_{gs}$ . On the outer loop, the  $V_{ds}$  value was set manually by the hint shown on the LCD screen. Inner loop ( $V_{gs}$ ) was iterated fully automatically. On each measurement point all voltages (including power supply) and  $I_d$  current was measured and placed in the UART output stream. Herewith, given and measured control voltages were compared, and in the case of more than negligible discrepancies – measurement process was interrupted with error message. On the controlling computer side all data was stored to the file by the "picocom" – terminal program. All data was represented in the textual form – one line per measurement point. The acquired  $I_d(V_{ds}, V_{gs})$  dependencies in the 3-D form are represented in the figure 4.

**Figure 4:** The experimental  $I_d(V_{ds}, V_{gs})$  dependencies for the selected JFET samples.

# 5. Model synthesis

The main goal of this research is to provide suitable for the declared goals  $I_d(V_{ds}, V_{gs})$  dependence. According to numerous previous analytical and approximation-based studies [9,10–13], this dependence is complex, consists of several regions, and requires an essential number of parameters. So, the new model cannot depend on a small number of parameters. Simultaneous parametric identification of complex non-linear models, taking info into account cut-off areas and different modes – extremely non-trivial task, where small measurement errors can lead to fully inadequate model construction. So, to diminish the risk of such wrong modeling, a sequential approach, based on physical background was implemented.

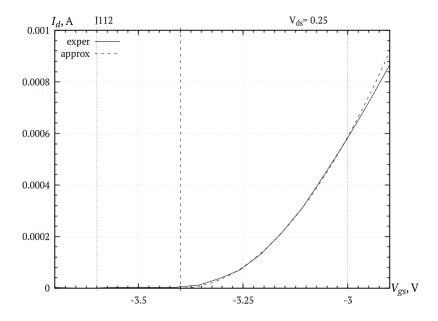

First of all, we should obtain  $V_{gs0}(V_{ds})$  dependence – as cut-off voltage  $V_{gs0}$  can be measured independent of all other parameters. This dependence is often neglected, but ignorance of this really small change can lead to wrong identification of other parameters. But the measurement of  $V_{gs0}$  using its formal definition can provide us wrong results – as small current fluctuations can be treated as the start of real current. To achieve more adequate results, we can use the known fact [4,5,6] that the initial  $I_d(V_{gs})$  dependence at constant  $V_{ds}$  resembles a quadratic function with good precision, and approximate this function. During this approximation, we must keep maximum  $I_d$  to really small values, approximately < 0.5 mA, to prevent usage of other modes. On the contrary, too low current limit can decrease precision too, as in this case we use smaller amounts of data points and measure small current, where errors have essential influence. The inner gnuplot "fit" command was used to make this approximation.

**Figure 5:** Experimental and approximated  $I_d(V_{gs})$  dependence for J112 JFET.

We approximate drain-source current (fig. 5) in this region as

$$I_{d}(V_{gs}) \approx \begin{cases} 0, & V_{gs} < V_{gs0} \\ k_{q}(V_{gs} - V_{gs0})^{2}, & \text{otherwise} \end{cases}$$

(1)

We should obtain  $V_{gs0}$  and  $k_q$  values for every observed  $V_{ds}$  value. To simplify expressions, we will denote  $V_{gs}$ – $V_{gs0}$  as  $V_{gr}$ .

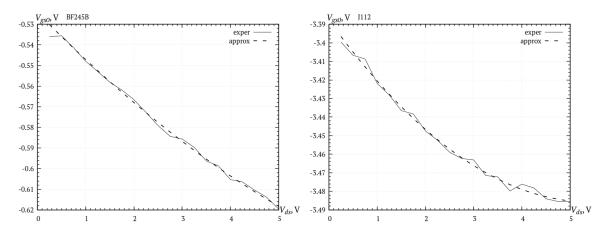

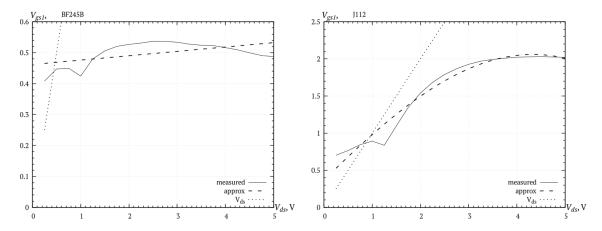

Examination of the acquired in the previous step dependence  $V_{gs0}(V_{ds})$  for all samples allows up to make a conclusion, what a simple second-order polynomial is enough for adequate representation (fig. 6).

**Figure 6:** Experimental and approximated  $V_{gs0}(V_{ds})$  dependencies for J112 and BF245B JFETs.

So, for the  $V_{gs0}(V_{ds})$  we will use following approximation:

$$V_{gs0}(V_{ds}) \approx a_{gs0} + V_{ds}b_{gs0} + V_{ds}^2c_{gs0},$$

(2)

where  $a_{gs0}$ ,  $b_{gs0}$ ,  $c_{gs0}$  – coefficients, describing particular JFET. In the datasheets the  $a_{gs0}$  coefficient denoted as  $V_{gs(off)}$ , other coefficients are ignored in most cases.

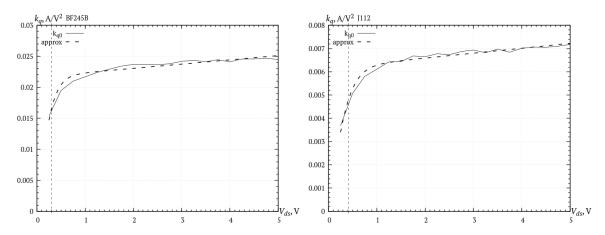

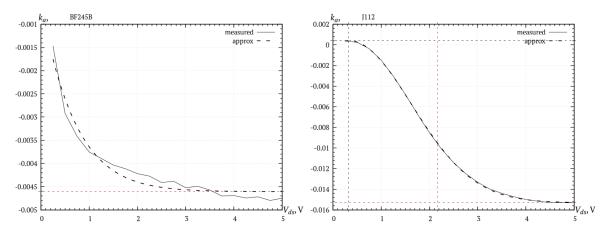

From the representation (1) we can derive one more approximation:  $k_q(V_{ds})$  (fig. 7).

**Figure 7:** Experimental and approximated  $k_q(V_{ds})$  dependencies for J112 and BF245B JFETs.

After several iterations, the following approximation was chosen for  $k_q(V_{ds})$ :

$$k_{q}(V_{ds}) = a_{kq} \left( \tanh \left( \frac{V_{ds}}{V_{kq}} \right) + c_{kq} V_{ds} \right), \tag{3}$$

where  $a_{kq}$ ,  $V_{kq}$ ,  $c_{kq}$  – parameters, obtained during function fitting.

Having obtained this starting point, we must choose the next stage: approximate  $I_d(V_{gs})$  with constant  $V_{ds}$  and combine these approximations over different  $V_{ds}$ , or in the opposite direction. Both approaches were tested, and the first one demonstrated best results. So, let's examine the  $Id(V_{gs})$  form. Or better,  $I_d(V_{gr})$  to use results from (1). In most non-degenerate cases we can observe 3 parts: cut-off, quadratic part, and near-no-linear part. The transition from cut-off to quadratic part can be done without problem. It seems natural to make transmission from the quadratic to linear part with the condition of equal derivatives in the left and right side from the junction point. This approach

leads to errors - may be not significant in common cases, as on frequently used schematics this region is often avoided [7,13]. Moreover, in most models the condition of the junction point is chosen as  $V_{ds}=(V_{gs}-V_{gs0})$ . But the results of measurements show us that this assumption is not correct, and such models may be used only outside junction point. So, the following approximation is proposed:

$$k_a = a_{ka} + b_{ka} \left[ \exp \left( -\frac{\left( V_{ds} - c_{ka} \right)^2}{d_{ka}^2} \right) - 1 \right],$$

(4)

$$k_b = a_{kf} \left( \tanh \left( \frac{V_{ds}}{V_{\alpha}} \right) + k_{fl} V_{ds} \right), \tag{5}$$

$$V_{gs2} = \frac{k_b}{2k_a},\tag{6}$$

$$D = 4 k_a k_q + k_b^2, (7)$$

$$D_a = \sqrt{|D|}, (8)$$

$$D_q = \sqrt{|D|},\tag{8}$$

$$d_p = \frac{D_q}{2k_a},\tag{9}$$

$$V_{gs2} = \frac{k_b}{2k_q} + d_p, (10)$$

$$X_d = V_{gs2} + d_p, \tag{11}$$

$$k_{c} = \frac{x_{d} = V_{gs2} + d_{p},}{4k_{a}k_{q} + k_{b}^{2}},$$

$$k_{c} = \frac{4k_{a}k_{q} + k_{b}^{2}}{4k_{q}V_{gs2}^{2} - 4k_{b}k_{d} - 4k_{a}},$$

(11)

$$V_{gs1} = \frac{k_b x_d + 2 k_a}{2 k_q x_d - k_b}, \text{ (limit to > 0)}$$

(12)

$$I_{d}(V_{gr}, V_{gs1}, k_{q}, k_{a}, k_{b}, k_{c}, x_{d}) = \begin{cases} 0, & V_{gr} < 0 \\ k_{q}V_{gr}^{2} & 0 < V_{gr} < V_{gs1} \\ k_{a} + k_{b}V_{gr} - k_{c}\sqrt{max}\left(x_{d} - V_{gr}, 0\right) & V_{gr} \ge V_{gs1} \end{cases}$$

(13)

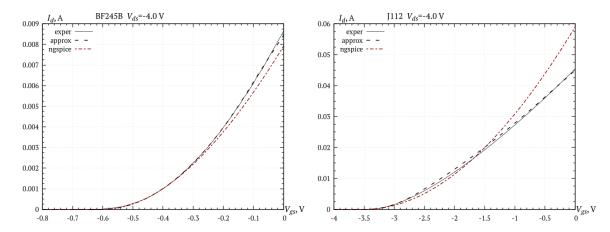

The results of such approximation are presented on figure 8.

Figure 8: Comparisons of the approximation (4) with experimental data for J112 and BF245B JFETs.

As was mentioned before, these approximations make sense only for one fixed  $V_{ds}$ . To provide a more general and common model, we must try to find quite simple, but usable dependencies for all coefficients from (4).

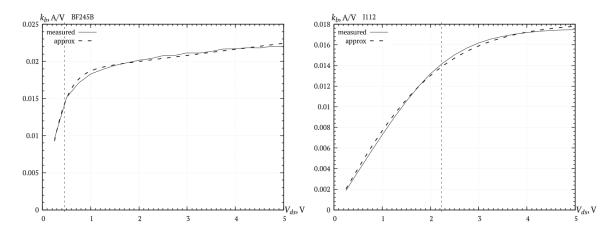

The  $k_b(V_{ds})$  approximation (5) is not a trivial, but gives us good results: The results are represented on figure 9.

**Figure 9:**  $k_v(V_{ds})$  approximations for J112 and BF245B JFETs.

The  $V_{gs1}$  coefficients approximated as follows:

$$V_{gs1} = k_{gs1} \left( \tanh \left( \frac{V_{ds} - V_{gs10}}{V_{gs11}} \right) + k_{gs1l} \left( V_{ds} - V_{gs10} \right) \right).$$

(14)

The results are represented on figure 10. These results demonstrates, that using  $V_{ds}$  value as  $V_{gs1}$  is possible only in very rare conditions, as the experimental  $V_{gs1}(V_{ds})$  curves, in general, have the only intersection point.

**Figure 10:**  $V_{gsI}(V_{ds})$  approximations for J112 and BF245B JFETs.

The results of the  $k_a$  approximation (4) are represented on figure 11.

**Figure 11:**  $k_a(V_{ds})$  approximations for J112 and BF245B JFETs.

All of the coefficients in equations (4)—(14) should be provided in the case of new model utilization. The equations under consideration have relatively complex form, but provide us sufficient approximation level for the essentially different samples.

# 6. Results and verification

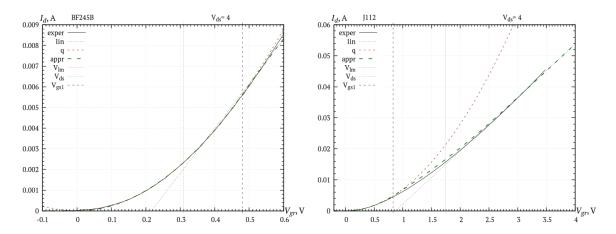

To verify the usability of the new model we need to compare experimental data with simulation, taking into account coefficients, obtained in one point, but using (5)–(7) expressions. It is impossible to correctly represent simulation errors on the one plot, so slices on  $V_{ds}$ =const and  $V_{gs}$ =const will be represented.

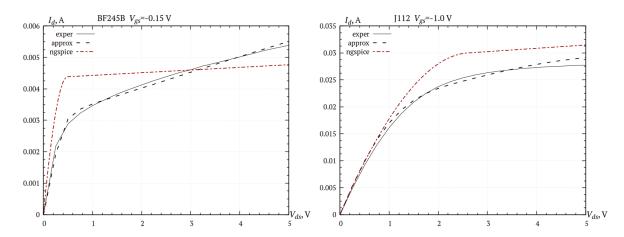

In the figure 12 comparison results was presented at  $V_{gs}$ =const.

**Figure 12:** Experimental data, new model, and ngspice model simulation results  $V_{gs}$ =const.

In the case of the using standard SPICE model parameters, the results of the simulations were incomparable – even they cannot be represented in the same plot with experimental data. To achieve satisfactory results with old model, the corresponding parameters from the new model were used. This is not the sign of the unusability of the old model – precision simulation often requires parameters adjustment. But even with these adjustments the proposed model has significant difference from the classic one. The difference in the  $I_d$  values reached 20%, whereas new model give near the 5% in the worst case. Moreover, new model provided qualitative better conforming to the experimental data, which, in turn, gives us the possibility not only to acquire more precise simulation results in the common ranges, but to extrapolate simulation out of these bounds.

**Figure 13:** Experimental data simulation results  $V_{ds}$ =const.

These plots demonstrate not so eye-visible differences in comparison with the previous ones, but the common result is the same. This is not unusual, as they uses the same data, but in the different point of view. The error levels have the save values too.

It is worth to take into account, that presented plots are the small and less precise part of the overall experimental data. For the each of the four samples 40—200 data sets (slices) where acquired and simulated. Most of these slices demonstrate approximately 1% of the simulation error. As an exception to the rule, it should be noted that measurements are made at very low currents, when the relative accuracy of the change drops, as well as at extreme current values, when heating becomes significant.

The curve comparison results allow us to statement, that new model provides not perfect, but really good approximation for the different JFET samples. Some of the required features was acquired by the creation process, other – as a result of sequential approximation. The exact form of equations (4)–(13) may be treated as somewhat "magical", but it was created after large amount of "try—check" iterations. As a drawback, new model requires more parameters, but it is unavoidable in the case of different complex dependencies.

The similar results were obtained with other voltage ranges and different samples. No essential simulation errors were detected. On the 3-D plots only the minimal eye-visible differences can be observed. These figures are not provided here, as no distinct visual differences are observed in comparison with Figure 4.

# 7. Conclusions

Existing JFET models are generally adequate, but do not provide us with some significant properties, especially near boundary conditions. The new model allows us to decrease errors and provides better qualitative conformity with the experimental data. The proposed method for the sequential measurements of the model parameters essentially simplifies the process, reducing the number of simultaneously calculated parameters. The proposed model, in spite of some drawbacks, provides a better level of conformity with this real data. The main drawback, in our opinion, is the somewhat artificial origin of equations (4)–(17). Also, it is worth taking into account that due to equipment limits, the thermal characteristics of the new model still remains to be investigated. This can be a task for future research. The hardware and software developed during this research can supply researchers with the required background to conduct measurements in a nearly automatic mode and collect data for both model synthesis and verification. Moreover, the acquired results can allow us to improve measurement hardware to diminish the detected drawbacks.

# **Declaration on Generative AI**

The authors have employed the Gemini AI tool for partial proofreading.

# References

- [1] Linear Systems. JFET Circuit Design: A Schematics Library and Application Notes. Linear Systems. Jul 1, 2024.

- [2] P. Horowitz, W. Hill, The art of electronics, 3rd ed., Cambridge University Press, Cambridge, 2015.

- [3] A. Guda, A. Zimoglyad, Simultaneous parametric identification for the coupled relaxation generators system, Proc. Int. Sci. Tech. Conf. Information Technologies in Metallurgy and Machine Building, Dnipro, 2022, pp. 261–264. doi:10.34185/1991-7848.itmm.2022.01.057.

- [4] J. Hertz, Design Considerations for Using JFETs in IoT and Low-Power Devices, Wevolver, 2025. URL: https://www.wevolver.com/article/design-considerations-for-using-jfets-in-iot-and-low-power-devices

- [5] Bernstein, J. Miller, Raanan Kelley, William Ward, Paul, Low-noise MEMS vibration sensor for geophysical applications, Microelectromechanical Systems Journal 8 (2000) 433–438. doi:10.1109/84.809058.

- [6] Jake Hertz, The Future of JFETs in a Digital-Dominated World, Wevolver, 2025 URL: https://www.wevolver.com/article/the-future-of-jfets-in-a-digital-dominated-world.

- [7] H. Diego, J. Huang, Emulation of junction field-effect transistors for real-time audio applications, IEICE Electronics Express 13(12), (2016) 1–11. doi:10.1587/elex.13.20160288.

- [8] C. Zhang, M. Zhang, Y. Li, Measurement and Simulation of Magnetic Properties of Nanocrystalline Alloys under High-Frequency Pulse Excitation, Materials 16 (2023) 2850. doi:10.3390/ma16072850.

- [9] A. E. Parker, D. J. Skellern, An improved FET model for computer simulators, IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst., vol. 9, no. 5, pp. 551–553, 1990. doi:10.1109/43.55175.

- [10] I. Richer, R.D. Middlebrook, Power-law nature of field-effect transistor experimental characteristics, Proceedings of the IEEE, vol. 51, no. 8, pp. 1145–1146, Aug. 1963. doi:10.1109/PROC.1963.2457

- [11] C. Hartgring, An accurate JFET/MESFET model for circuit analysis, Solid-State Electronics, Vol. 25, Issue 3, pp. 233–240, 1982. doi:10.1016/0038-1101(82)90113-7.

- [12] P. Neudeck, Technical Primer on Design and SPICE Modeling of Circuits for NASA Glenn SiC JFET IC, Version 12 Prototype Wafer Run Part 1: SiC JFET Behavior and SPICE Modeling, NASA Glenn Research Center, Cleveland, Ohio USA, 2019.

- [13] D. Divekar, FET modeling for circuit simulation, Valid Logic Systems, Inc., Kluwer academic publishers, Volume 192, 1998. doi:10.1007/978-1-4613-1687-9.

- [14] Zhang, Ruizhe, Liu Jingcun, Li Qiang, Pidaparthi, Subhash, Edwards Andrew, Drowley Cliff, Zhang Yuhao, Breakthrough Short Circuit Robustness Demonstrated in Vertical GaN Fin JFET, in: IEEE Transactions on Power Electronics, Volume 37, Issue 6, June 2022, pp. 6253–6258. doi:10.1109/TPEL.2021.3138451.

- [15] Wong, W. W.; Liou, J. J., JFET circuit simulation using SPICE implemented with an improved model, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Volume 13, Issue 1, 1994, 105-109. doi:10.1109/43.273745.

- [16] P. Nenzi, The NGSPICE circuit simulator: An open platform for simulation and modelling, Dresden: Electronic design automation, 2014.

- [17] Erdei, Zoltan Iordache, Mihai Niculae, Dragos Stanculescu, Marilena Grib, Alexandru, The Use of S Parameters in Two-Port Analogue Networks Stability Analysis, IOP Conference Series: Materials Science and Engineering, 749, 012031, (2020). doi:10.1088/1757-899X/749/1/012031.

- [18] R. Sytnyk, Vik. Hnatushenko, V. Hnatushenko, Decentralized Information System for Supply Chain Management Using Blockchain, IntelITSIS 2022: Proc. of the 3rd Intern. Workshop on

- Intelligent Information Technologies & Systems of Information Security, Vol-3156, 587–598, 2022. http://ceur-ws.org/Vol-3156/?fbclid=IwAR25gkEK7r5iMV4jK7WNyR\_yvXq\_bXrCEb6D-aN2xbHLnJ8Rr2dLOr6T1Jc.

- [19] V. Kuznetsov, Microstrip Line Modeling Taking into Account Dispersion Using a General-Purpose SPICE Simulator, Low Power Electron. Appl 15, 42, (2025). doi:10.3390/jlpea15030042.

- [20] Nałęcz, M., SPICE-Compatible Circuit Models of Multiports Described by Scattering Parameters with Arbitrary Reference Impedances, Electronics 13, 2260, (2024). doi:10.3390/electronics13122260.

- [21] Kelp K, Wright D, Stephens J, Dickens J, Mankowski J, Shaw Z, Neuber A., Modeling Pulsed Magnetic Core Behavior in LTspice, Electronics, 14(12) (2025) 2335. doi:10.3390/electronics14122335.

- [22] Kelp, K., Wright, D., Stephens, J.; Dickens, J.; Mankowski, J., Shaw, Z., Neuber, A., Modeling Pulsed Magnetic Core Behavior in LTspice, Electronics 14, 2335, (2025). doi:10.3390/electronics14122335.

- [23] Shekh-Abed, A., Enhancing Learning in Microelectronic Circuits: Integrating LTspice Simulations and Structured Reflections in a Design Project, Educ. Sci 15, 1045, (2025). doi:10.3390/educsci15081045.

- [24] Kumar, Kundan Saxena, Vikram, LTspice Simulation Analysis for Loss Estimation of GaN MOSFET based Class E Resonant Inverter, 16, (2022). doi:10.1109/GlobConPT57482.2022.9938227.

- [25] H. Hackl, J. R. Lopera, D. Klien, M. Gholizadeh, S. Sadeghi, B. Auinger, On the Simulation of Conducted Emission of a Flyback Converter using LTSpice, 2024 International Symposium on Electromagnetic Compatibility, EMC Europe, Brugge, Belgium, (2024) 682-687. doi:10.1109/EMCEurope59828.2024.10722256.

- [26] K. Kanakgiri, D. Ishan Bhardwaj, B. Sai Ram, S. V. Kulkarni, A Circuit-Based Formulation for Soft Magnetic Materials Using the Jiles–Atherton Model, in IEEE Transactions on Magnetics, vol. 60, no. 10, 2024, pp. 1-7, Art no. 7301107. doi:10.1109/TMAG.2024.3452593.

- [27] M. Brinson, V. Kuznetsov, Extended behavioural device modelling and circuit simulation with Qucs-S, International Journal of Electronics 105(3), (2017) 412–425. doi:10.1080/00207217.2017.1357764.

- [28] BF245A; BF245B; BF245C N-channel silicon field-effect transistors, Netherland: NXP Semiconductors, 1996. URL: https://www.nxp.com/docs/en/data-sheet/BF245A-B-C.pdf.

- [29] J111, J112 JFET Chopper Transistors N-Channel Depletion J111, J112, J113 datasheet. ON Semiconductor, 2006. URL: https://www.onsemi.com/pdf/datasheet/j111-d.pdf.

- [30] JFET Switching Transistors N-Channel MMBF4391L, 14th ed, Onsemi, 2024. URL: https://www.onsemi.com/download/data-sheet/pdf/mmbf4391lt1-d.pdf.

- [31] J. Poirier, A very small C interpreter, 2015. URL: https://github.com/jpoirier/picoc.

- [32] RD6006 a buck step down direct voltage power supply unit, Joy-it, 2020. URL: https://joy-it.net/en/products/jt-rd6006.

- [33] Precision Instrumentation Amplifier Precision Instrumentation Amplifier AD8221, Norwood: Analog Devices, 2011. URL: https://www.analog.com/media/en/technical-documentation/data-sheets/ad8221.pdf

- [34] P. Mohindru, Electronic Circuit Analysis using LTSpice XVII Simulator: A Practical Guide for Beginners (1st ed.), CRC Press. 2021. doi:10.1201/9781003199489.